## **Research Summary**

Yuan-Hao Chang Deputy Director / Research Fellow / Professor Institute of Information Science, Academia Sinica

## **Research Interests**

- Emerging Memory Technologies

- Non-volatile Memories

- Memory/Storage Systems

- Embedded Systems

- Operating Systems

## **Next-generation Memory/Storage Systems**

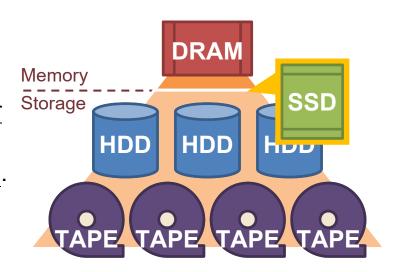

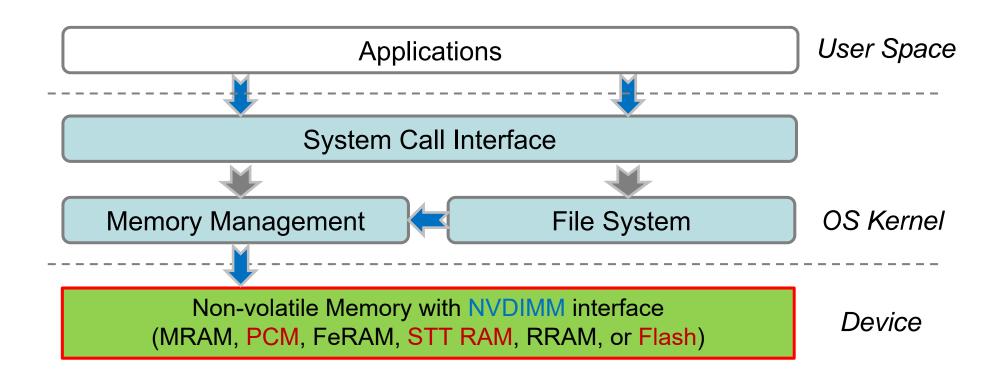

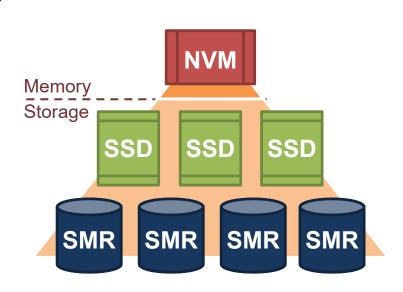

### Present:

- DRAM: Main memory

- Solid-state Drive (SSD): Cache/buffer for high performance environments

- Hard Disk (HDD): Main storage media.

- Magnetic tapes: Deep data <u>archiving</u>

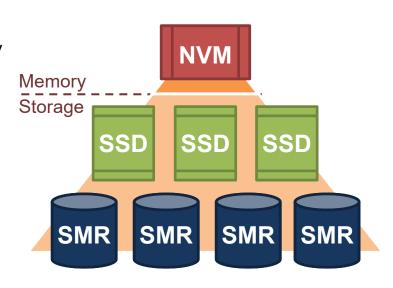

### Foreseeable Future:

- Non-volatile memory (NVM): Enlarge the scalability of in-memory computing

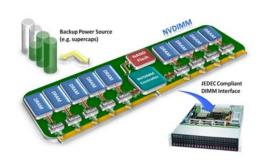

- Optane DIMM, NVDIMM, Process-in-Memory

- SSDs: Take over the <u>main storage</u> media

- Reasons: Density ↑ and cost ↓

- OCSSD, ZNS-SSD, Z-NAND, Optane

- HDDs & Tapes: Replaced by new magnetic recording technologies

- Objectives: Density ↑ and cost ↓

- Promising Candidate: SMR

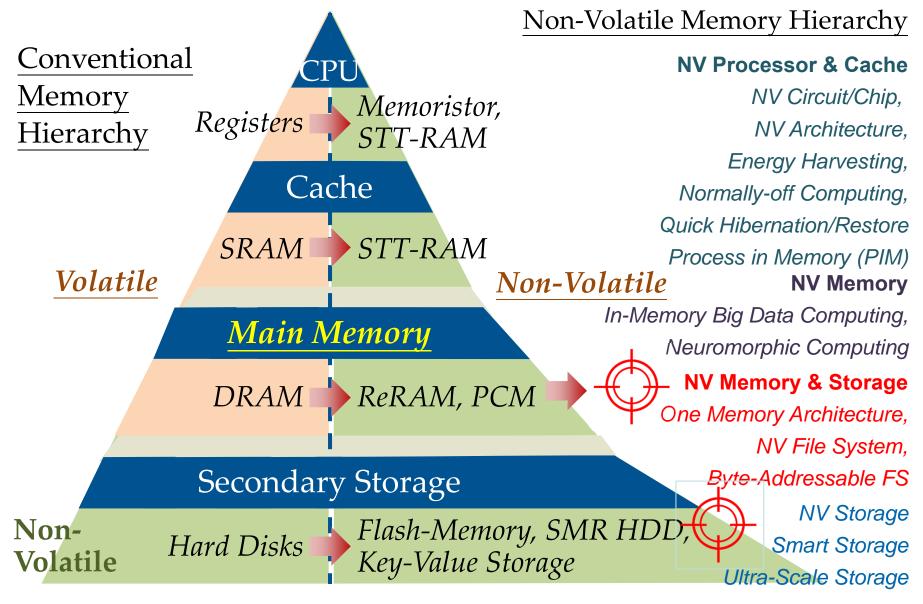

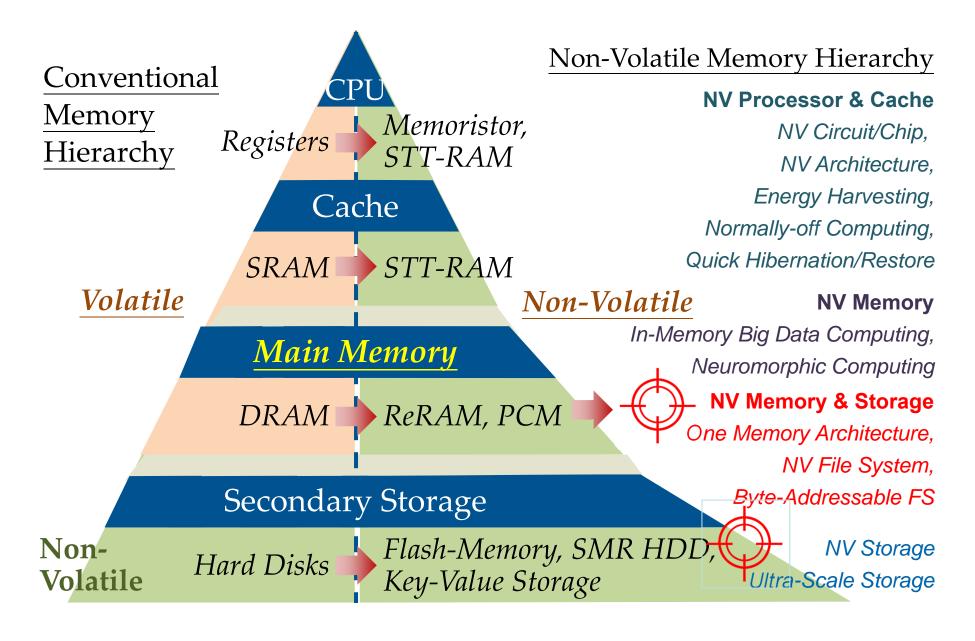

# Non-volatile Computing - Key Technology for Future IoTs

### **Research Directions**

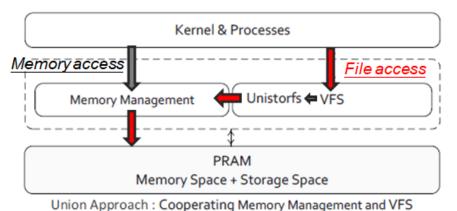

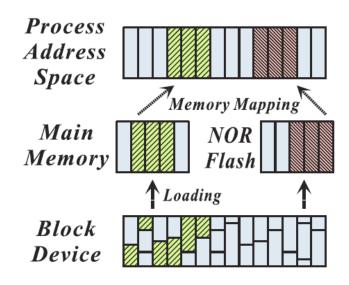

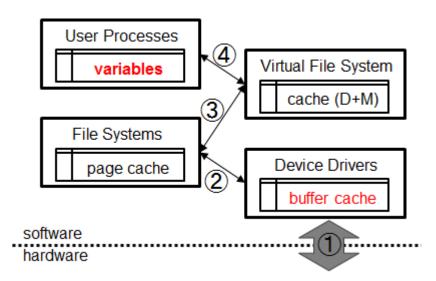

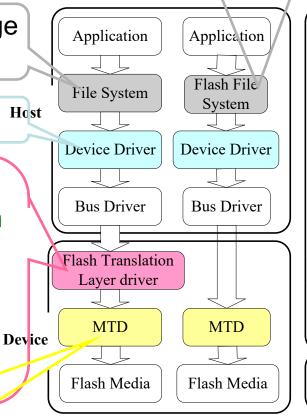

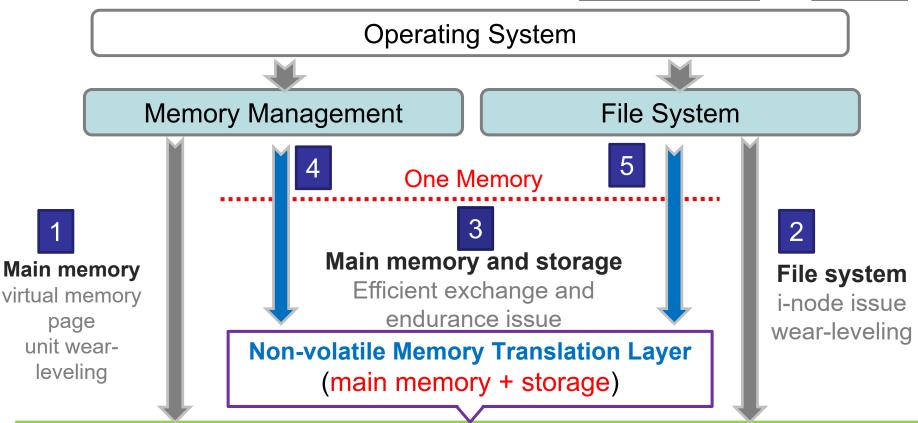

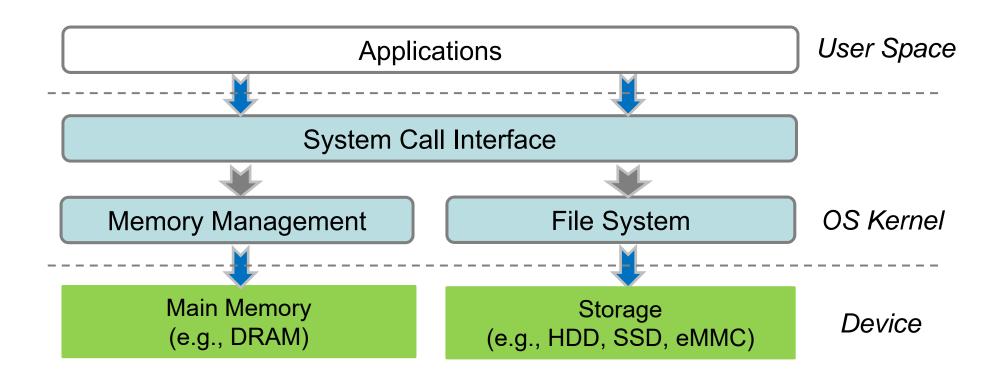

- Software: Non-Volatile System Software

- Most researches are based on the existing operating system designs.

- Memory Space: Managed by the memory management.

- Storage Space: Managed by the file systems.

- New non-volatile operating system and system software are needed by the non-volatile computing environment.

- The objective is to get rid of unnecessary software stacks (e.g., page cache, swap).

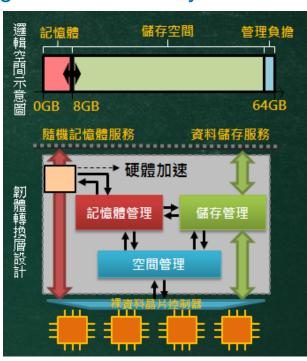

- System: Non-Volatile Systems

- System in a Chip (SiC): Control units + memory + storage are all in a chip.

- Process-in/near-memory (PIM): Computing + Memory + Storage

- Self-sustainable Sensor Nodes (Green IoT)

- Instant backup & restore capabilities of NV processors.

- Low standby power of NV memory (& storage).

- Intermittent systems (Energy harvesting systems).

- Storage (including file systems):

- Approximate storage

- Smart storage (CXL)

- UPMAN

- Application (supported by Memory/Storage):

- E.g., DNA sequencing, graph processing, random forest

## **Research Summary 2022**

# 1. Storage Systems - Flash Drives and SMR Disks

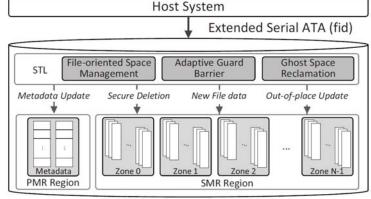

# File-Oriented Fast Secure Deletion for SMR Drives (IEEE TCAD'22, DAC 2019)

- Observation

- Existing secure deletion approaches are inefficient

- File systems have no knowledge of the data layout on the storage device

- Storage devices are not aware of the file information in file systems

- This inefficiency is exaggerated on shingled magnetic recording (SMR) drive

- Goal: Enable file-oriented fast secure deletion on sequential-write-constraint SMR drives

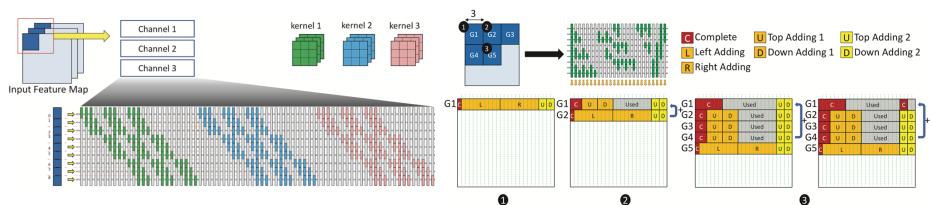

- Main Idea

- Minimize secure deletion overhead

- Adaptive guard barrier mechanism

- Manage storage space with file awareness

- File-oriented space management design

- Enhance the space utilization

- Free space reclamation scheme

Secure Deletion Latency Reduction: 8660x Space Overhead: 14.21%

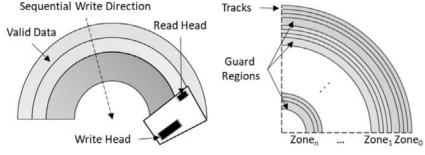

Sequential-Write-Constrained SMR Drive

Reclaim 1 - S % of ghost space from each file

- Shuo-Han Chen, Chun-Feng Wu, Ming-Chang Yang, and <u>Yuan-Hao Chang</u>, "A File-Oriented Fast Secure Deletion Strategy for Shingled Magnetic Recording Drives," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 41, no. 8, pp. 2463-2476, Aug. 2022.

- Shuo-Han Chen, Ming-Chang Yang, Yuan-Hao Chang, and Chun-Feng Wu, "Enabling File-Oriented Fast Secure Deletion on Shingled Magnetic Recording Drives," ACM/IEEE Design Automation Conference (DAC), Las Vegas, Nevada, USA, Jun. 2-6, 2019. (Top Conference)

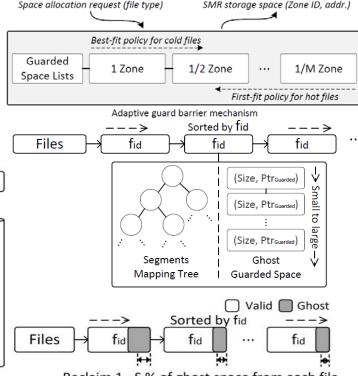

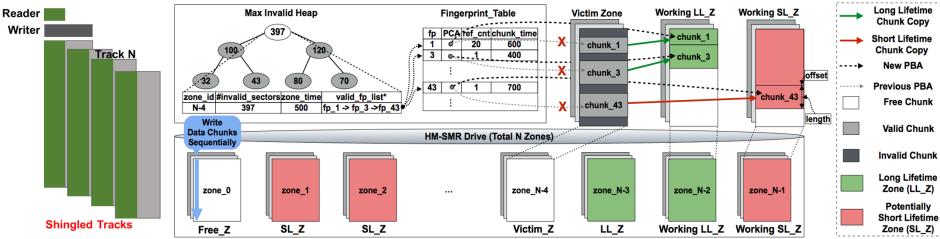

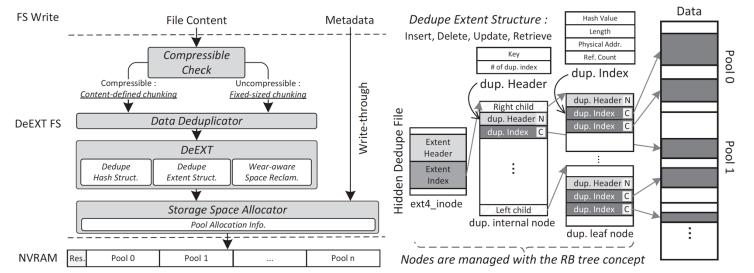

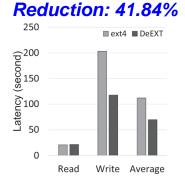

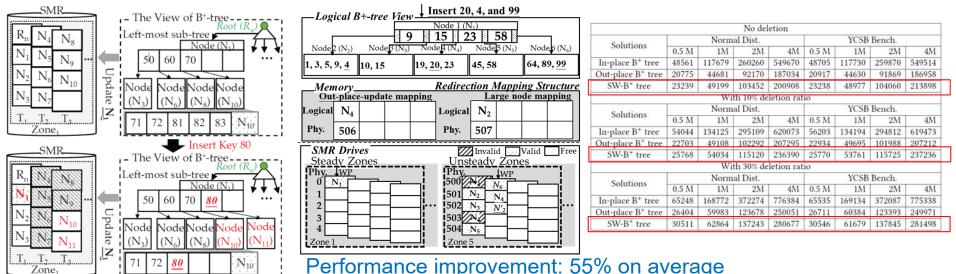

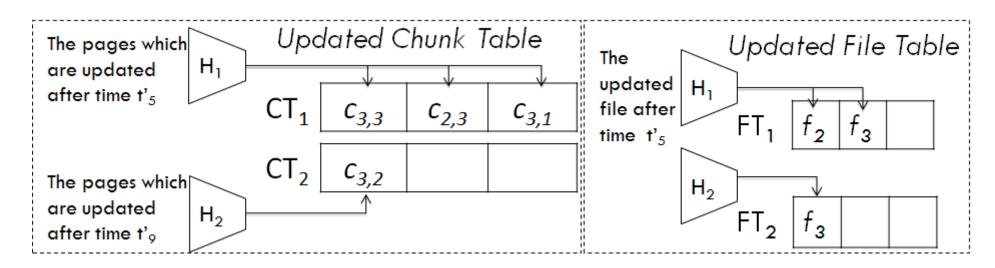

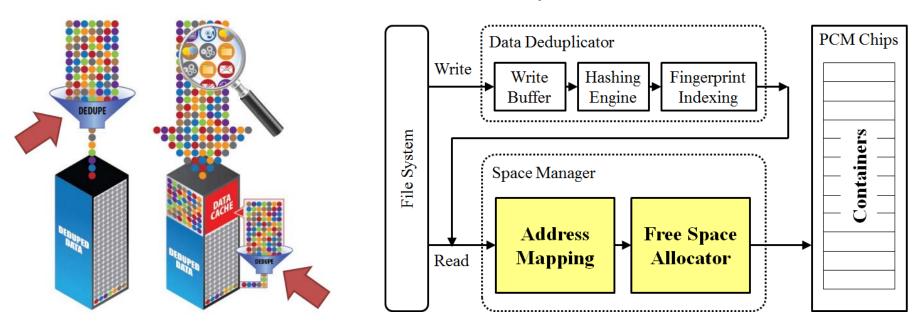

## **SMR-Aware Deduplication**

- We are among the pioneers to propose an <u>SMR-aware deduplication design</u> to improve the run time performance for SMR disks with considering (1) the SMR write constraint and (2) the deduped chunk lifetime/behavior. (IEEE TCAD'22, DAC'18)

- This design advocates a vertical integration solution by managing the host-managed SMR drives with deduplication system.

- The idea is to predict and separate "chunk lifetime" based on the semantic information.

- The proposed design was evaluated by the famous Skylight disk emulation tool and proved to improve performance for 82%.

- Chun-Feng Wu, Martin Kuo, Ming-Chang Yang, and Yuan-Hao Chang, "Performance Enhancement of SMR-based Deduplication SystemsIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 41, no. 9, pp. 2835-2848, Sep. 2022.

- Chun-Feng Wu, Ming-Chang Yang, and Yuan-Hao Chang, "Improving Runtime Performance of Deduplication System with Host-Managed SMR Storage Drives," ACM/IEEE Design Automation Conference (DAC), San Francisco, USA, Jun. 24-28, 2018. (Top Conference)

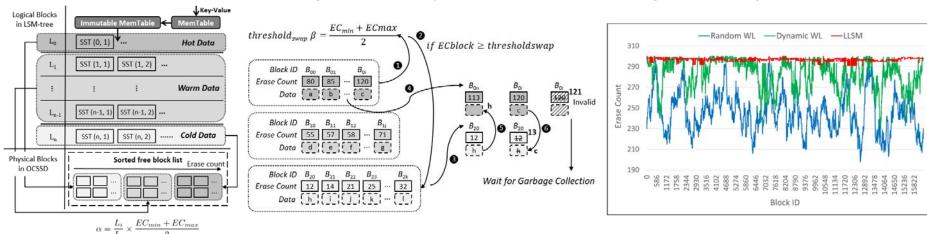

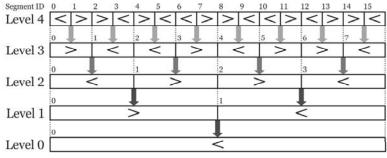

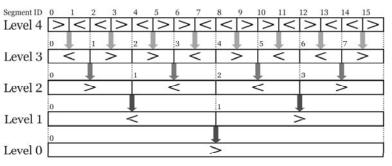

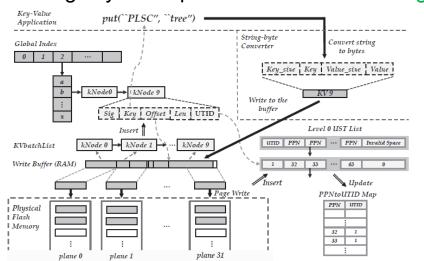

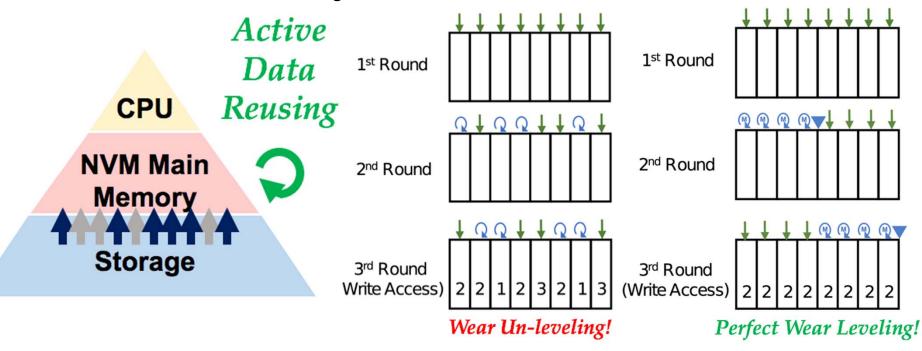

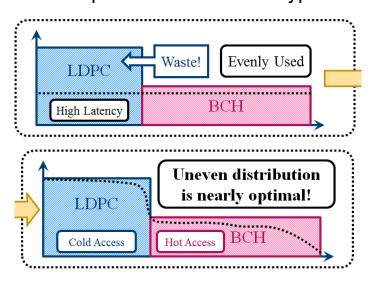

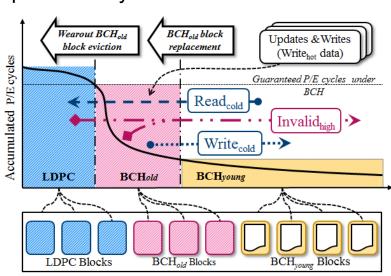

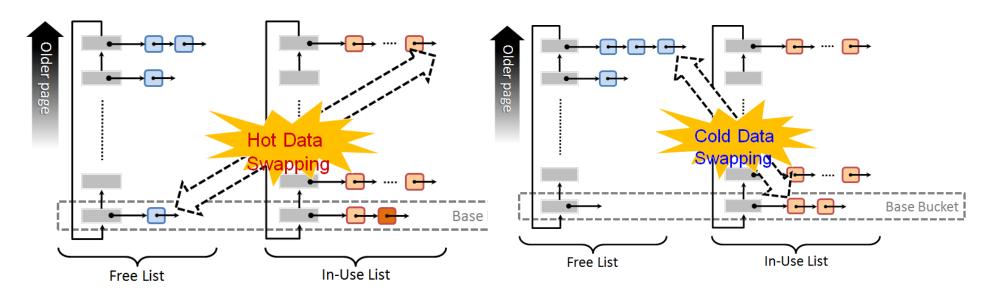

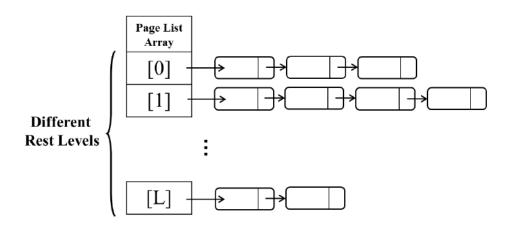

### LLSM: A Lifetime-Aware Wear-Leveling for LSM-Tree on NAND Flash

(IEEE TCAD'22, CASES'22)

- Lifetime is a critical issue for flash memory-based SSDs. However, the existing wear-leveling strategies fail to solve the endurance issues caused by LSM-tree based key-value stores on SSDs

- We design a lifetime-aware wear-leveling for LSM-tree on flash memory-based SSDs to prolong the SSD lifetime via OCSSD

- Level-Aware Block Allocation: properly allocate the data in the LSM-tree to the memory blocks according to the data hotness based on the LSM-tree levels

- Proactive Block Swapping: intelligently swap the old and young blocks to prevent uneven wear-out among the memory blocks in terms of long-term usage

- Extensive results show that the proposed LLSM improves the SSD lifetime up to 21.7%

- Dharamjeet, Yi-Shen Chen, Tseng-Yi Chen, Yuan-Hung Kuan, and <u>Yuan-Hao Chang</u>, "LLSM: A Lifetime-Aware Wear-Leveling for LSM-Tree on NAND Flash Memory," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 41, no. 11, pp. 3946-3956, Nov. 2022. (Integrated with ACM/IEEE CASES'22)

- Dharamjeet, Yi-Shen Chen, Tseng-Yi Chen, Yuan-Hung Kuan, and Yuan-Hao Chang, "LLSM: A Lifetime-Aware Wear-Leveling for LSM-Tree on NAND Flash Memory," ACM/IEEE International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES), Hybrid-Shanghai, China, Oct. 7-14, 2022. (Journal Track, Integrated with IEEE TCAD) (Top Conference)

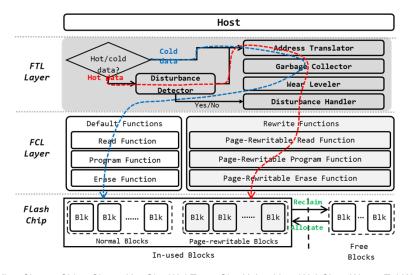

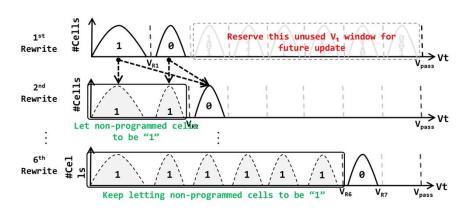

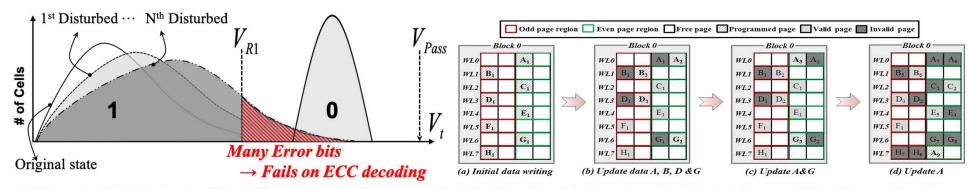

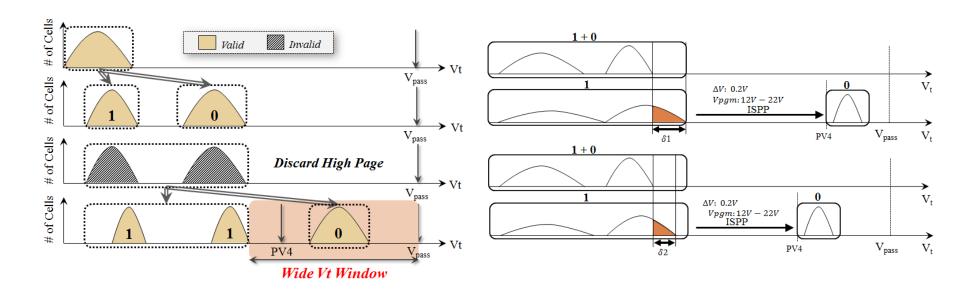

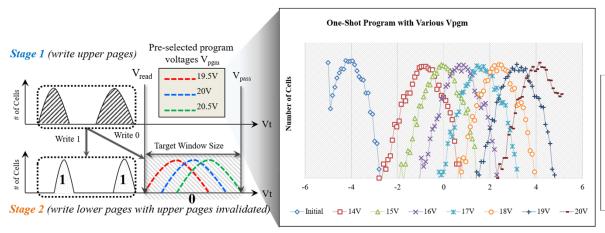

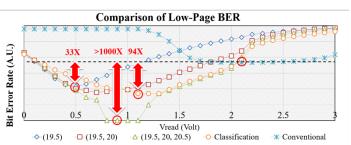

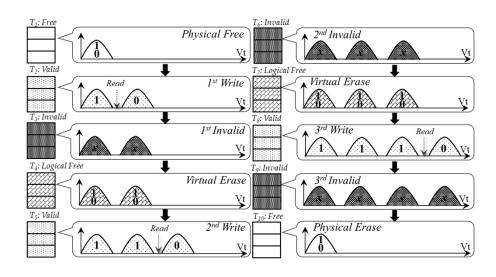

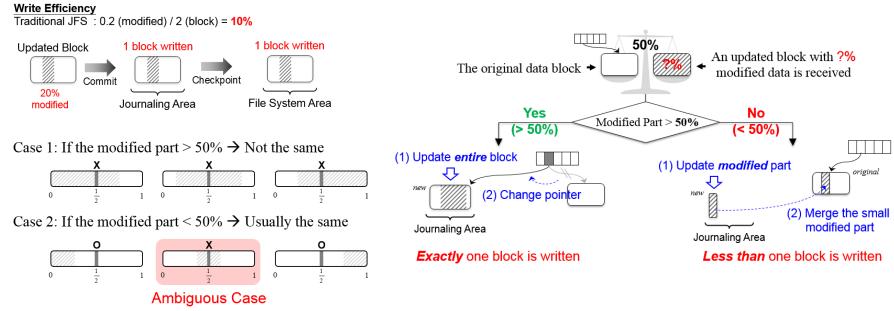

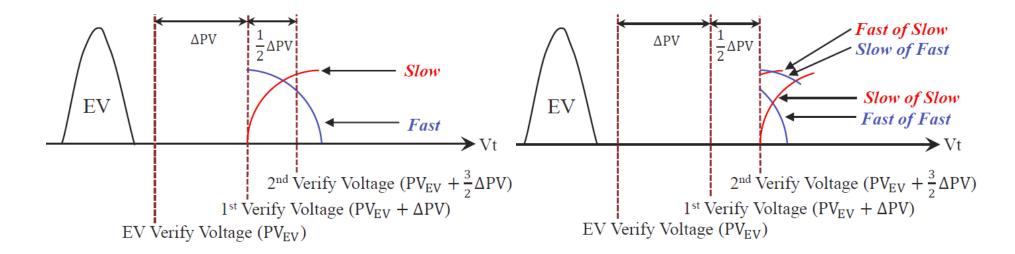

## **Enduring More Data through Enabling Page Rewrite Capability on MLC Flash**

Goal

(SAC 2022)

- To sustain more and more data in flash-based storage system

- To minimize the adverse effect of effective disturbance while taking advantage of page-rewriteprogramming

- Effective disturbance a page with a lower number of rewrites was disturbed because of rewriting an adjacent page with a higher number of rewrite

#### Main Idea

- The in-used blocks are divided into normal blocks and page-rewritable blocks and the idea is to increase the likelihood of generating invalid data as much as possible on those page-rewritable blocks that enable page rewrite

- Storing write-cold data to normal blocks and storing write-hot data to page-rewritable blocks

- To address the disturbance problem

- in-place rewrite rewriting the same data to the same page can increase its Vt and make it less susceptible to the disturbance

- page migration moving data to other pages that does not contain less valid data

Yu-Ming Chang, Chien-Chung Ho, Che-Wei Tsao, Shu-Hsien Liao, Wei-Chen Wang, Tei-Wei Kuo, and <u>Yuan-Hao Chang</u>, "On Enduring More Data Through Enabling Page Rewrite Capability on Multi-level-cell Flash Memory," ACM Symposium on Applied Computing (SAC), Virtual Conference, Apr. 25-29, 2022.

## 2. NVM Main Memory and Storage

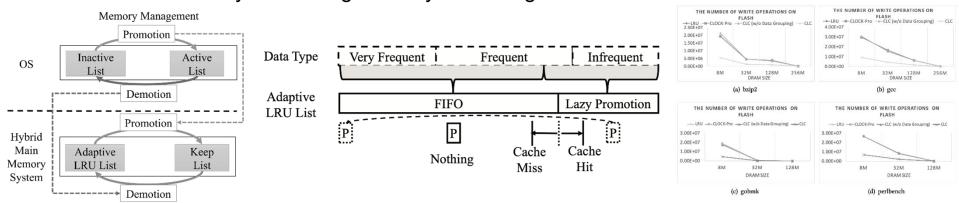

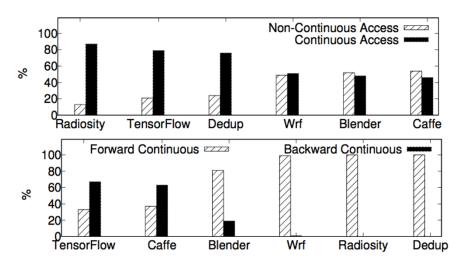

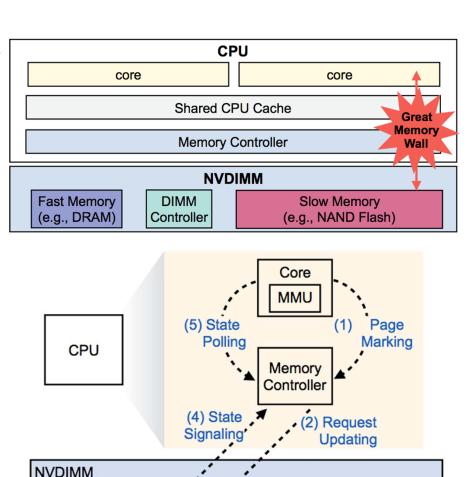

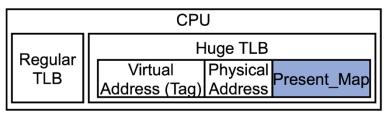

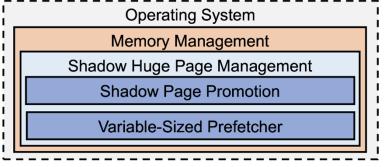

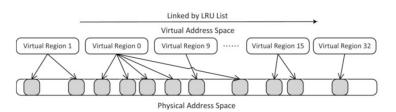

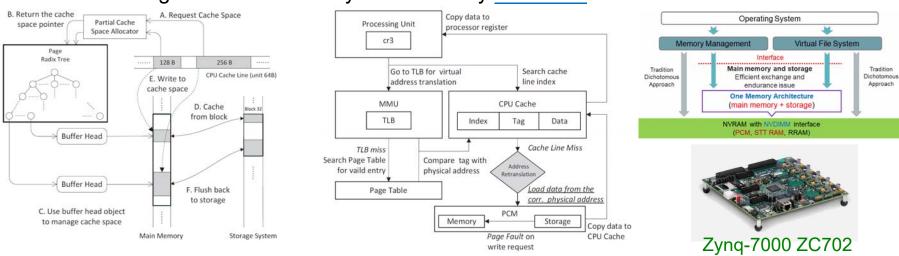

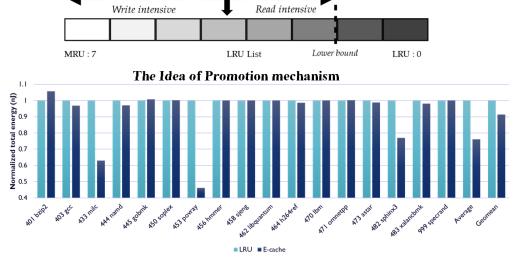

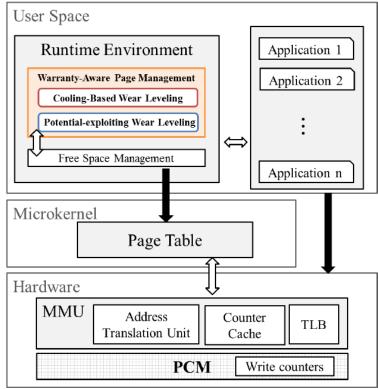

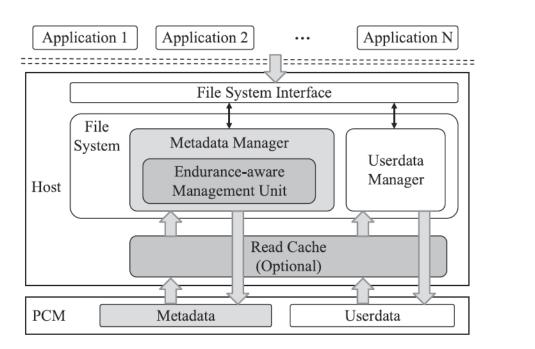

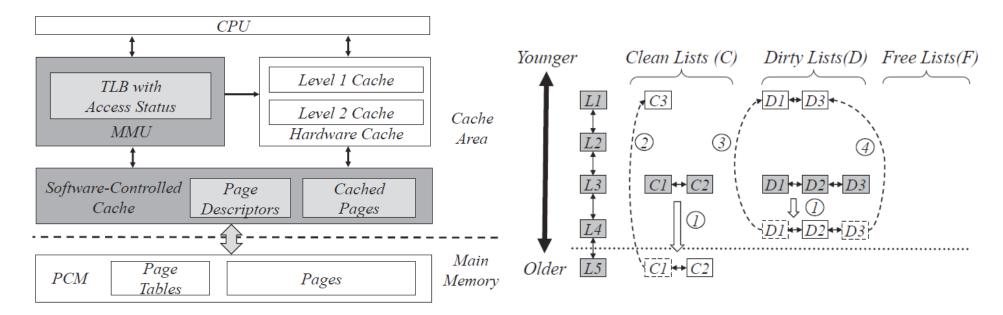

## Rethinking the Interactivity of OS and Device Layers in Memory Management (ACM TECS'22)

#### Observation:

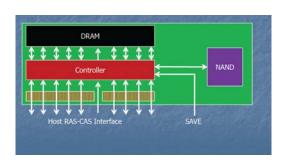

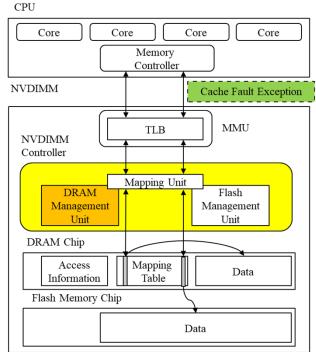

The hybrid main-memory module uses DRAM as the cache of NVMs to enhance its performance and lifetime. However, it also introduces new design challenges in both the OS and the memory module.

### · Goal:

Rethinking the interactivity of OS and hybrid main-memory module, and propose a <u>cross-layer cache design</u> to optimize the DRAM cache's hit ratio and minimize the time overhead on the data movement between DRAM and NVM.

#### Main Idea:

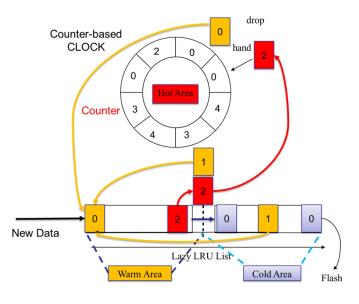

- Keep List maintains the recent frequently accessed data information from the operating system to optimize the hit ratio of the DRAM cache.

- Adaptive LRU List dynamically adjusts the length of the FIFO list and the lazy promotion list based on recent access behavior to avoid unnecessary management operations.

- Data Grouper takes advantage of NVM's block-size read/write feature to reduce the writes to flash memory without significantly sacrificing the DRAM cache hit rate.

<sup>-</sup> Tse-Yuan Wang, Chun-Feng Wu, Che-Wei Tsao, Yuan-Hao Chang, Tei-Wei Kuo, and Xue Liu, "Rethinking the Interactivity of OS and Device Layers in Memory Management," ACM Transactions on Embedded Computing Systems (TECS), vol. 21, no. 4, pp. 42:1-42:21, July 2022.

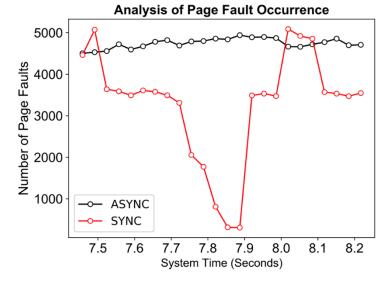

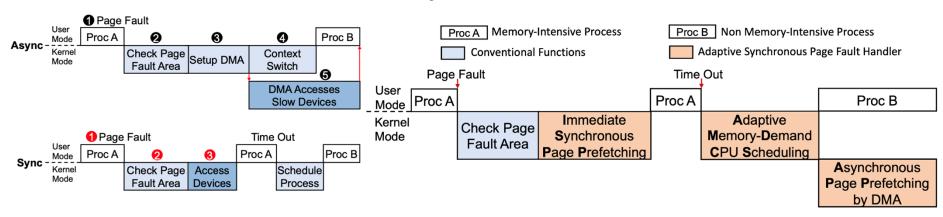

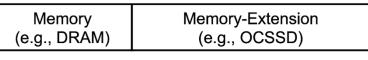

## **Exploring Synchronous Page Fault Handling**

### [IEEE TCAD'22, CODES'22 (Best Paper Award)]

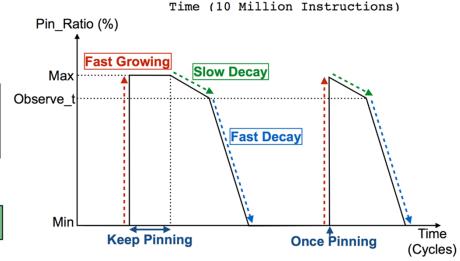

### Observation

- Async page fault handler: Stable results.

- Sync page fault handler: Number of page faults fluctuates.

- High Peak: Reconstructing working set.

- Low Bottom: After reconstructing working set.

#### Goal

Deal with the working set contention issue so as able to remove the peak of page faults and reduce the occurrence of page faults.

#### Main Idea

- Adjust the designs of CFS CPU scheduler to fit sync page fault handling.

- Prefetch and reconstruct the working set.

- Yin-Chiuan Chen, Chun-Feng Wu, Yuan-Hao Chang, and Tei-Wei Kuo, "Exploring Synchronous Page Fault HandlingIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 41, no. 11, pp. 3791-3802, Nov. 2022. (Integrated with ACM/IEEE CODES+ISSS'22)

- Yin-Chiuan Chen, Chun-Feng Wu, Yuan-Hao Chang, and Tei-Wei Kuo, "Exploring Synchronous Page Fault Handling," ACM/IEEE International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), Hybrid-Shanghai, Oct. 7-14, 2022. (Journal Track, Integrated with IEEE TCAD) (Top Conference)

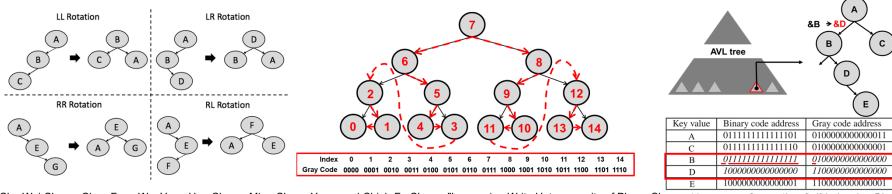

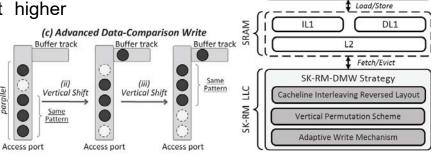

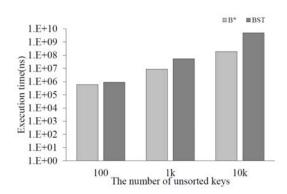

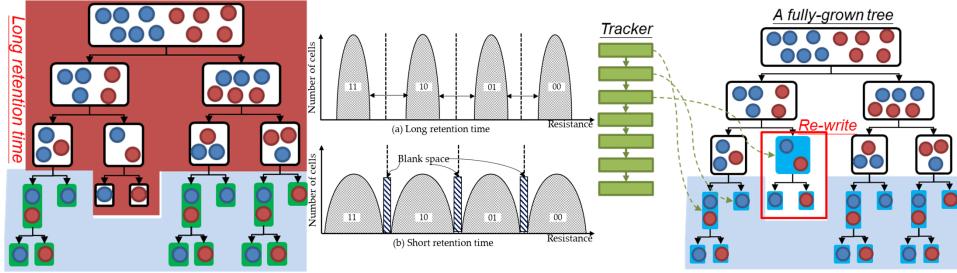

## Search Tree Redesign on Phase Change Memory - Rethinking Self-balancing Binary Tree over PCM

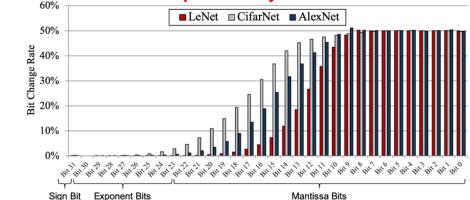

- We exploit the <u>write heterogeneity of phase change memory</u> to improve the performance of a self-balancing binary search tree by reducing the rotation overheads of tree balancing (IEEE TCAD in 2022, ASP-DAC 2018)

- Observations:

- Rotations of tree balancing are not arbitrary: Some nodes have stronger relation

- Data-comparison writes eliminate unnecessary bit flips: Reducing the number of bit flips can reduce the write energy and/or latency

- A write-heterogeneity-aware management scheme of the AVL tree structure is developed for binding nodes with considerations of their relation

- The relation among nodes of an AVL tree is analyzed by examining possible rotations

- Our depth-first alternating traversal (DFAT) algorithm is then designed for tree indexing

- Gray code is leveraged by DFAT to reduce the average number of bit flips per write

- Che-Wei Chang, Chun-Feng Wu, Yuan-Hao Chang, Ming-Chang Yang, and Chieh-Fu Chang, "Leveraging Write Heterogeneity of Phase Change Memory on Supporting Self-balancing Binary Tree," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 41, no. 6, pp. 1757-1770, Jun. 2022.

- Chieh-Fu Chang, Che-Wei Chang, <u>Yuan-Hao Chang</u>, and Ming-Chang Yang, "Rethinking Self-balancing Binary Search Tree over Phase Change Memory with Write Asymmetry," in ACM/IEEE Asia and South Pacific Design Automation Conference (ASP-DAC), Jeju Island, Korea, Jan. 22-25, 2018.

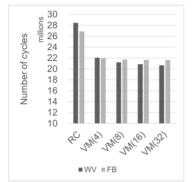

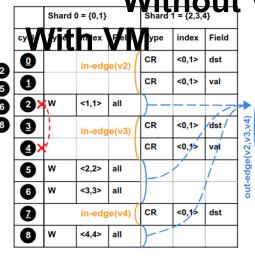

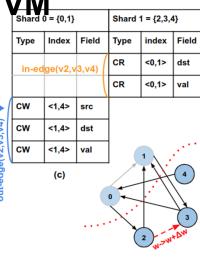

## GraphRC: Accelerating Graph Processing on Dual-addressing Memory with Vertex Merging

#### Observation

(ICCAD 2022)

- Graph processing task can be accelerated on dual-addressing memory.

- Memory accesses suffer from a low utilization rate due to the size mismatching between graph data and the cache block size.

#### Solutions

- Propose vertex merging (VM) that improves the cache block utilization rate by merging memory requests from consecutive vertices.

- Then, identify data dependencies inherent in a graph that limits the effectiveness of VM.

Propose aggressive vertex merging (AVM) that merges vertices based its importance not its data dependency.

**AVM** reduces execution time by **73.27%** while **VM** offers **22.51%** reduction.

28

26

24 22 20

18

16

(a) VM applied to PR algo. on WV (b) AVM applied to PR algo. on and FB datasets. WV and FB datasets.

(b)

<sup>-</sup> Wei Cheng, Chun-Feng Wu, Yuan-Hao Chang, and Ing-Chao Lin, "GraphRC: Accelerating Graph Processing on Dual-addressing Memory with Vertex Merging," ACM/IEEE International Conference on Computer-Aided Design (ICCAD), San Diego, California, USA, Oct. 30 - Nov. 3, 2022. (Acceptance rate: 22.5%(132/586)) (Top Conference)

## Drift-tolerant Coding to Enhance the Energy Efficiency of MLC PCM

(ISLPED 2022)

- Resistance drift is a critical challenge of PCM. It may become more severe in MLC PCM because more states are represented by a cell.

- We design a drift-tolerant coding to improve the energy efficiency and resolve the resistance drift errors of MLC PCM without sacrificing the data accuracy

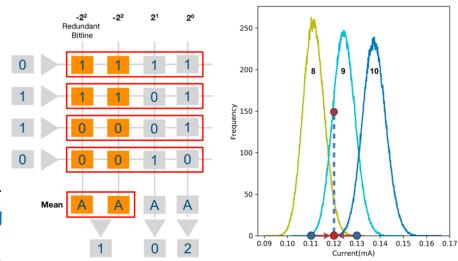

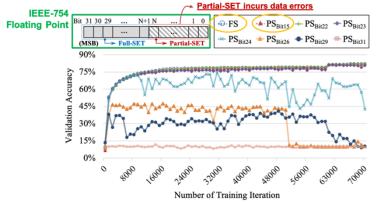

- <u>Drift-tolerant Code</u>: remap 3-bit datawords into 4-bit drift-tolerant codes to tolerate the resistance drift errors of MLC PCM when applies Partial-SET to accelerate PCM writes

- Write Process Segmentation: divide the write process into fast and slow write units to

improve the write performance of drift-tolerant coding ergy Consumption malized to Baseline) DT Codes **Drifted Codes** Data "01" drifts to "00" 000 0001 0000 1.5 Total Energy ( (Normalize 001 0101 0100 010 1001 1000 011 1101 1100 Fast Write Unit (FWU) 0 ~ 2.5 Slow Write Unit (SWU) 0 ~ ■ Baseline □ TriState-SET □ Enhanced WOM ■ DT Coding 100 1111 Time Program with No resistance drift Full-SET 1110 101 SWU SWU SWU SWU 0010 110 **01**10 Total Write Normalized to 111 0111 0011 Time Extensive results show that the drift-tolerant coding

reduces 6.2-17.1% energy consumption and 3.2-11.3% on MLC PCM

<sup>-</sup> Yi-Shen Chen, Yuan-Hao Chang, and Tei-Wei Kuo, "Drift-tolerant Coding to Enhance the Energy Efficiency of Multi-Level-Cell Phase-Change Memory" ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), Boston, MA, USA, Aug. 1-3, 2022. (Top Conference)

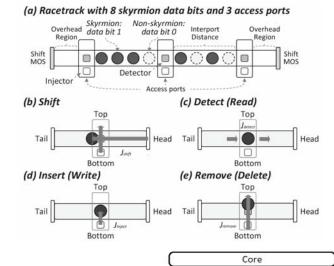

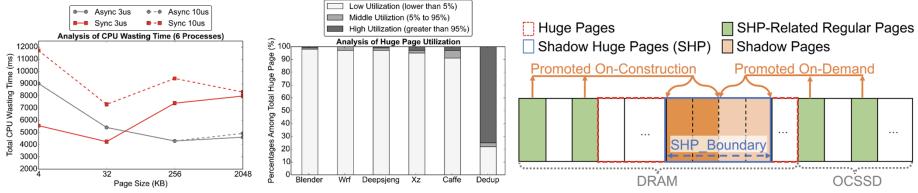

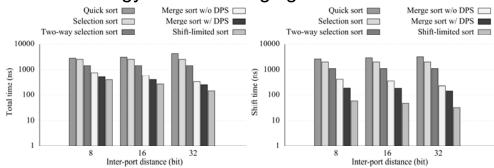

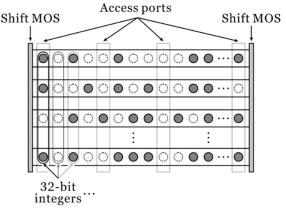

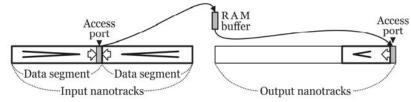

## **Evolving Skyrmion Racetrack Memory as Energy-Efficient Last-Level Cache Devices**

#### Observation:

- Skyrmion racetrack memory (SK-RM) stores data bits on the racetrack via skyrmions and relies on shift operations to read/write data bits.

- However, shift operations lead to unpredictable data access performance or excessive energy consumption

#### Goal:

- Drawing benefits from both the bit-interleaved and word-based mapping approaches

- Word-based mapping: Lower energy, but higher latency

- Bit-interleaved mapping: Lower latency, but higher energy

#### Main idea:

- Dual Write Mode (DWM) strategy

- Combine data write method of bit-interleaved and word-based mapping approaches

- Utilize the feature of shifting skyrmions across racetracks

- Include buffer tracks at each access ports

22.89% & 44.62% reduction in latency and energy consumption.

(ISLPED 2022)

- Ya-Hui Yang, Shuo-Han Chen, and <u>Yuan-Hao Chang</u>, "Evolving Skyrmion Racetrack Memory as Energy-Efficient Last-Level Cache Devices" ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), Boston, MA, USA, Aug. 1-3, 2022. (Top Conference)

# 3. Machine Learning Techniques with NVM

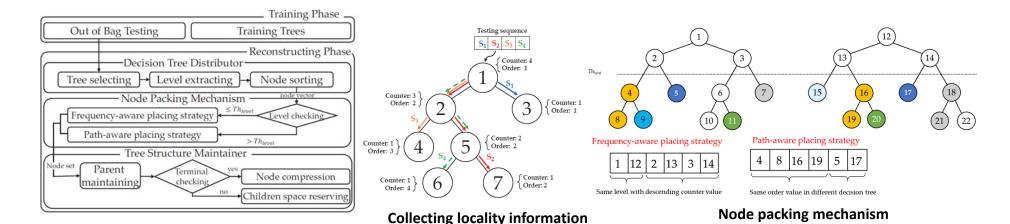

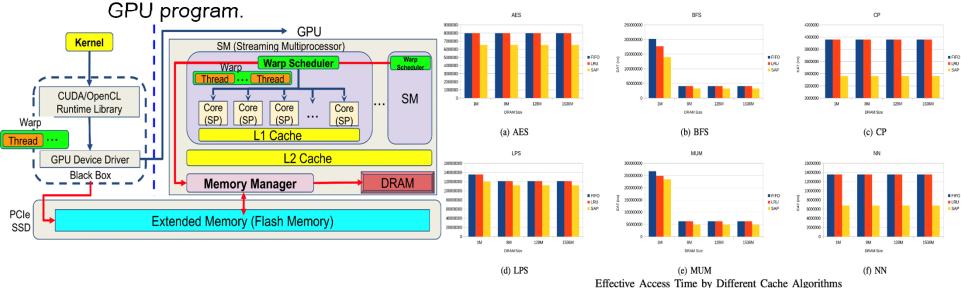

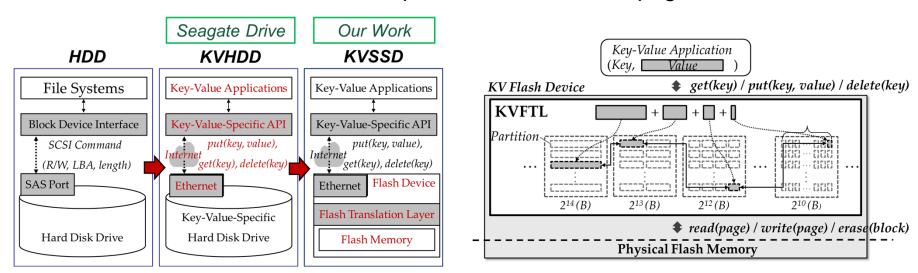

## Minimizing the Read Latency of Flash Memory to Preserve Inter-tree Locality in Random Forest

- Motivation: (ICCAD 2022)

- Data move between the limited main memory space and the flash storage frequently while inferencing in memory-limited embedded system.

- Goal:

- Reduce the swapping operations between DRAM and flash memory during inference

- Design philosophy

Overview of LaRF

- Reconstruct the trained RF model after training phase to pack the to-be-used-together nodes together in flash pages.

- Considering both intra- inter- locality to reconstruct the trained RF model

- Collecting the locality information in normal training process (OOB testing)

Yu-Cheng Lin, Yu-Pei Liang, Tseng-Yi Chen, <u>Yuan-Hao Chang</u>, Shuo-Han Chen, and Wei-Kuan Shih, "On Minimizing the Read Latency of Flash Memory to Preserve Inter-tree Locality in Random Forest," ACM/IEEE International Conference on Computer-Aided Design (ICCAD), San Diego, California, USA, Oct. 30 - Nov. 3, 2022. (Acceptance rate: 22.5%(132/586)) (Top Conference)

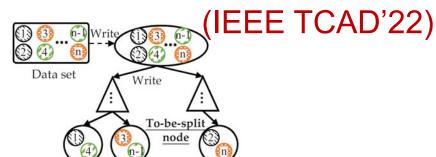

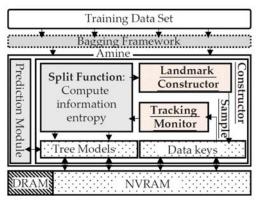

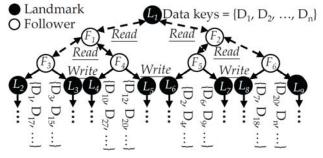

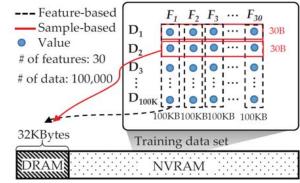

## Planting Fast-growing Forest with NVM (AMINE)

- Motivation:

- Heavy write traffic in random forest

- Write traffic may hurt both the performance and lifetime of NVRAM

#### Goal:

- Enable a faster random forest constructing method, and prolong the lifespan of NVRAM

- Design philosophy

- Replace partial writing operations by reading operation while construction a RF model

- Only keep the data index in landmark nodes, and the follower nodes read their data by the index stored in their previous landmark node.

- Change the manner to read data from dataset to limited DRAM

- Using sample-based access manner instead of feature-based access manner

The design philosophy of Amine.

Overview of Amine.

The difference between sample-based and feature-based readers.

<sup>-</sup> Yu-Pei Liang, Tseng-Yi Chen, <u>Yuan-Hao Chang</u>, Yi-Da Huang, and Wei-Kuan Shih, "Planting Fast-growing Forest by Leveraging the Asymmetric Read/Write Latency of NVRAM-based Systems," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 41, no. 10, pp. 3304-3317, Oct. 2022.

# 4. In/Near-Memory Processing with NVM

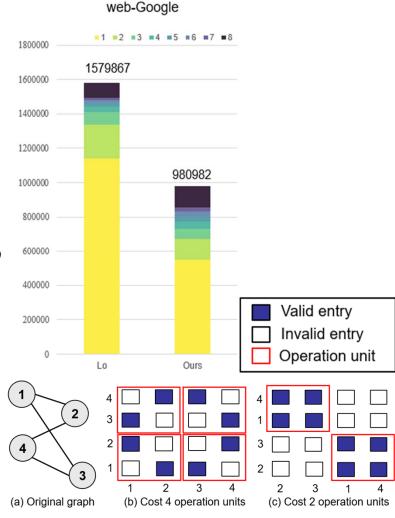

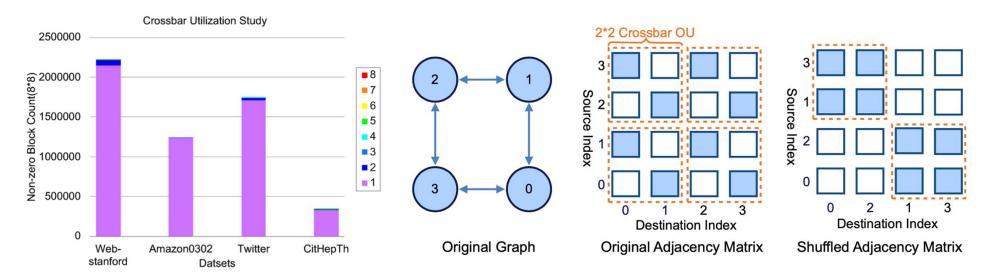

## SGIRR: Sparse Graph Index Remapping for ReRAM Crossbar Operation Unit

#### Observation

- Placing an adjacency matrix on the ReRAM crossbar array with operation units for accelerating matrix multiplication may lead to unnecessary operation units cost and undesirable energy dissipation.

- Reason: Most the real-world graphs are too sparse and discrete for the ReRAM crossbar array to utilize effectively, suffering from sparse matrix-vector multiplication (SpMV) problem.

#### Goal

Design an effective index remapping algorithm to minimize the total number of operation units in ReRAM crossbar arrays and energy consumption.

### Contribution

We propose a two-stage spatial-aware algorithm and an operation-unit-aware column filtering approach to derive the graph order permutation, achieving better crossbar operation unit usage and energy consumption than the existing work. (ICCAD 2022)

<sup>-</sup> Cheng-Yuan Wang, Yao-Wen Chang, and Yuan-Hao Chang, "SGIRR: Sparse Graph Index Remapping for ReRAM Crossbar Operation Unit and Power Optimization," ACM/IEEE International Conference on Computer-Aided Design (ICCAD), San Diego, California, USA, Oct. 30 - Nov. 3, 2022. (Acceptance rate: 22.5%(132/586)) (Top Conference)

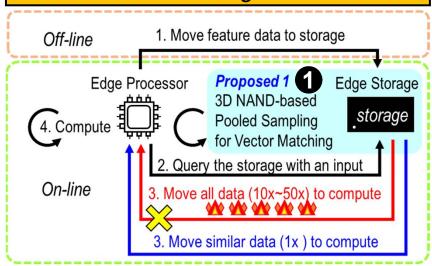

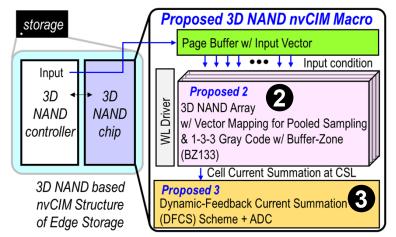

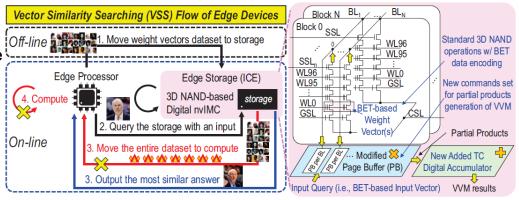

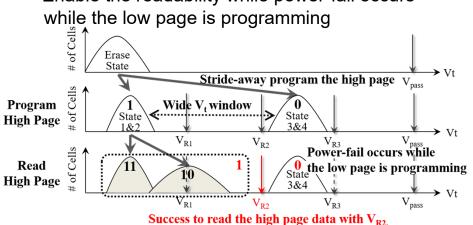

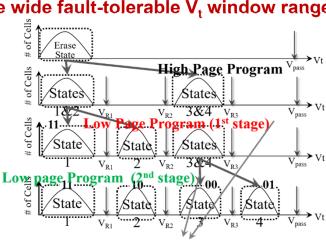

(ISSCC 2022)

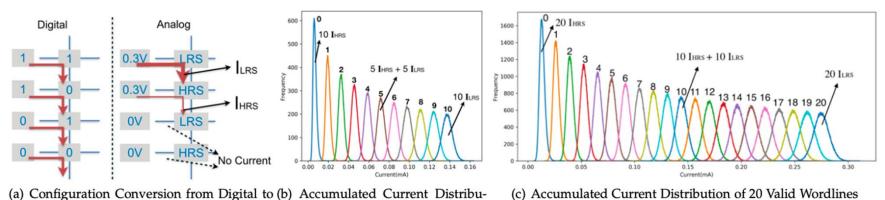

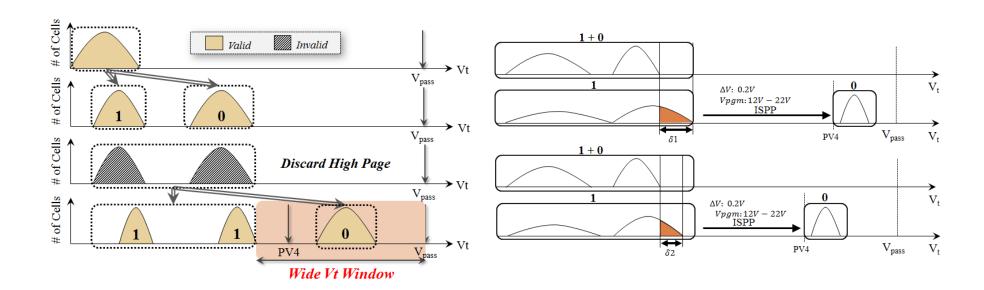

## 512Gb In-Memory-Computing 3D NAND Flash Supporting Similar Vector Matching Operations on Al Edge Devices

- Observation

- Existing vector similarity search (VSS) on edge devices is not inefficient

- Long search latency and large search energy due to large invalid data movement

- Exploiting 3D NAND with in-memory computing (IMC) for VSS will face two major challenges:

- A low-readout accuracy by using the wide range Vtlevel of cells

- The large-readout power consumption for the possible data-patterns.

- Goal: Enable 3D NAND-based IMC for similar vector matching to boost the VSS performance

- Main Idea

- 1 Adopted "pool sampling" as the major search algorithm

- $\vec{V}_{INPUT} \cdot \vec{V}_{INDEX_0} + \dots + \vec{V}_{INPUT} \cdot \vec{V}_{INDEX_K}$

- $= \vec{V}_{INPUT} \cdot (\vec{V}_{INDEX\_0} + \dots + \vec{V}_{INDEX\_K})$

- Reuse the selective-BL read function on page buffer with unary data format [HTLue'19:IEDM]

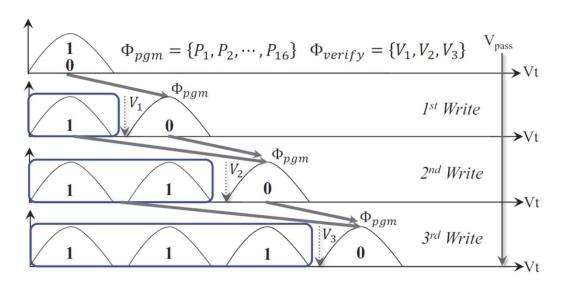

- A 1-3-3 Gray code with buffer zone (BZ133) for TLC cells, guarding against a low readout accuracy for VVM operation

- 3 Dynamic-feedback-based current-summation (DFCS) scheme to guard against the wide summation current range of VVM operations.

### VSS Flow of Edge Devices

Han Wen Hu, Wei-Chen Wang, Chung-Kuang Chen, Yung-Chun Lee, Bo-Rong Lin, Huai-Mu Wang, Yen-Bo Lin, Yu-Chao Lin, Chih-Chang Hsieh, Chia-Ming Hu, Yi-Ting Lai, Yuan-Hao Chang, Hsiang-Pang Li, Han-Sung Chen, Tei-Wei Kuo, Keh-Chung Wang, Meng-Fan Chang, Chun-Hsiung Hung, and Chih-Yuan Lu, "A 512Gb In-Memory-Computing 3D NAND Flash Supporting Similar Vector Matching Operations on Al Edge Devices." IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, California, USA, Feb. 20-24, 2022. (Top Conference)

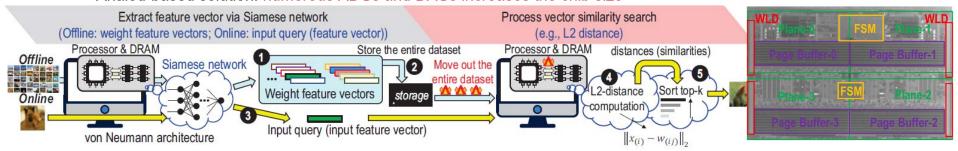

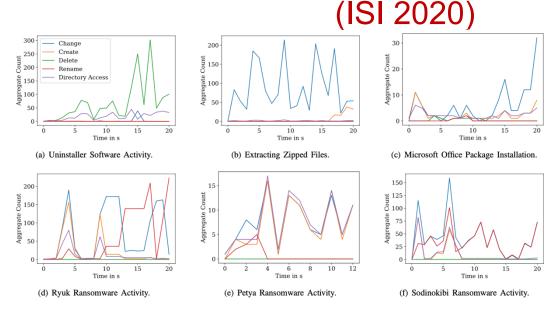

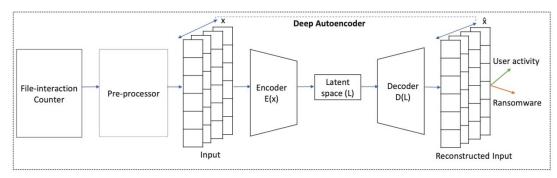

## ICE: An Intelligent Cognition Engine with NAND Processing-in-Memory for Vector Similarity Search

Observation

(MICRO 2022)

- Existing vector similarity search (VSS) on edge devices is not inefficient

- Long search latency and large search energy due to large invalid data movement

- Exploiting 3D NAND with nonvolatile in-memory computing (nvIMC) for VSS will face two major challenges:

- Digital-based solution: ECC is critical to the nvIMC design for VSS applications since it guarantees data reliability

- Analog-based solution: numerous ADCs and DACs increases the chip size

- Goal: Enable 3D NAND-based digital nvIMC to accelerate the VSS applications

- Main Idea

- Exploit bit-error tolerant data encoding to mitigate the bit-error influence

- Adopt modified page buffer to achieve single bit multiplication after computation unfolding

- Add a new two's complement accumulator to achieve sign-bit computations in accumulation state

- Propose a hierarchical top-n search to filter invalid data and output the most similar answer during conducting VSS applications

<sup>-</sup> Han-Wen Hu, Wei-Chen Wang, Yuan-Hao Chang, Yung-Chun Lee, Bo-Rong Lin, Huai-Mu Wang, Yen-Po Lin, Yu-Ming Huang, Chong-Ying Lee, Tzu-Hsiang Su, Chih-Chang Hsieh, Chia-Ming Hu, Yi-Ting Lai, Chung-Kuang Chen, Han-Sung Chen, Hsiang-Pang Li, Tei-Wei Kuo, Meng-Fan Chang, Keh-Chung Wang, Chun-Hsiung Hung, and Chih-Yuan Lu, "ICE: An Intelligent Cognition Engine with 3D NAND-based In-Memory Computing for Vector Similarity Search Acceleration," ACM/IEEE International Symposium on Microarchitecture (MICRO), Chiago, Illinois, USA, Oct. 1-5, 2022. (Top Conference)

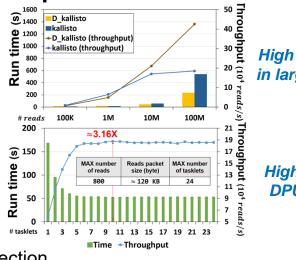

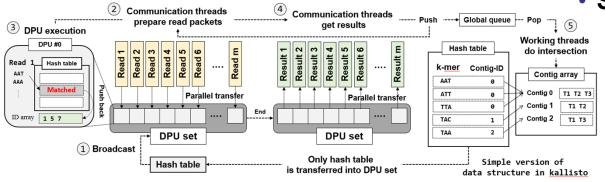

## RNA-seq Quantification on Processing in memory Architecture (DPU) (NVMSA 2022)

• **Goal**: We choose <u>RNA-seq quantification</u> to be a case study, <u>understanding</u> the characteristics of sequencing on <u>UPMEM DPU</u>.

### Concerns

- DPU constrains: e.g. no data sharing between DPUs

- Frequent data movement between CPU and DPU

- DPU-based software design

### Implementation

- Host CPU broadcasts the hash table to all DPUs

- Communication threads send read packets to DPU

- 3. Host CPU launches the DPU program

- 4. Communication threads get result back to host

- 5. Working thread will get a ID from queue and do intersection.

### Implementation Result

High throughput in large data size

High efficiency DPU program

### Suggestions / Observations

- UPMEM DPU system is a material suitable for large data size.

- Frequent data transfers is an overhead in DPU system.

- WRAM is expensive, we have to design the data flow carefully during DPU-based programming.

<sup>-</sup> Liang-Chi Chen, Shu-Qi Yu, Chien-Chung Ho, Yuan-Hao Chang, Da-Wei Chang, Wei-Chen Wang, and Yu-Ming Chang, "RNA-seq Quantification on Processing in memory Architecture: Observation and Characterization," IEEE Nonvolatile Memory Systems and Applications Symposium (NVMSA), Taipei, Taiwan, Aug. 23-25, 2022.

## 5. Intermittent Systems

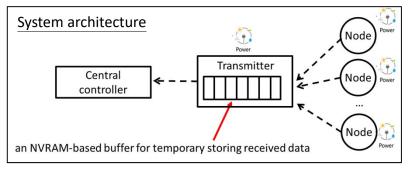

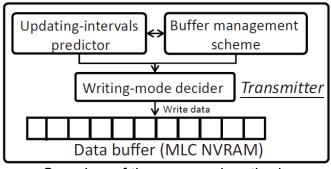

## Minimizing Age-of-Information of NVRAM-based Intermittent Systems (NVMSA 2022)

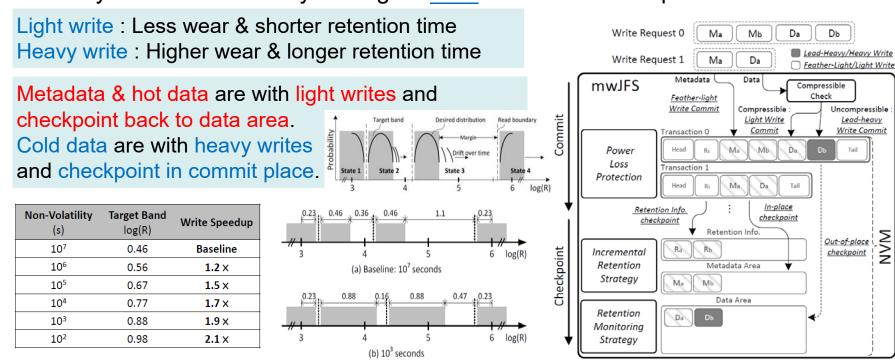

#### Motivation:

- Traditional replacement policy cannot minimize the Aol

- Even adopting the multi-level write, the energy still may be waste without considering the buffer replacement policy

#### Goal:

- Minimize the average AoI of the generated data of the sensor nodes.

- Design a buffer-replacement-policy-aware writing-mode decider

#### Main ideas

- Predict the node behavior

- Approximate average the updating interval

- Balance the update frequency of the sensor nodes to prevent the soaring of AoI.

- 1. Duplication Check 2. Updating-Frequency Balance

- Use the proper writing mode to write the data to NVRAM for further reducing the energy consumption

- using light write if the data frequently update and tends to be replaced

Replacing the old version?

Replacing the old version?

Writing the data to the buffer

Ves

Check the bit flag

Can find the data with 1s in the bit flag?

Replacing the first coming data

Ves

Replacing the first coming data

Replacing the first coming data

The bit flag?

Replacing the first coming data

Replacing the first coming data

The bit flag?

Overview of the proposed method

Buffer management scheme

<sup>-</sup> Hung-Yu Lin, Yu-Pei Liang, Shuo-Han Chen, <u>Yuan-Hao Chang</u>, Tseng-Yi Chen, and Wei-Kuan Shih, "Minimizing Age-of-Information of NVRAM-based Intermittent Systems," IEEE Nonvolatile Memory Systems and Applications Symposium (NVMSA), Taipei, Taiwan, Aug. 23-25, 2022.

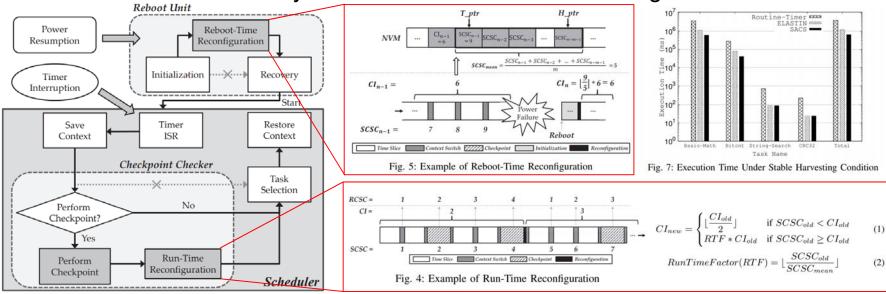

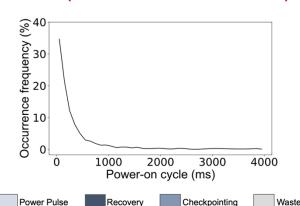

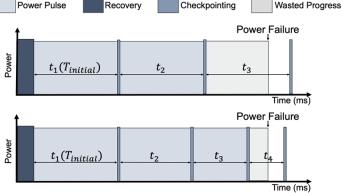

## SACS: A Self-Adaptive Checkpointing Strategy for Microkernel-Based Intermittent Systems

- In this work, we propose a new self-adaptive checkpointing strategy for improving the performance of microkernel-based intermittent systems. (ISLPED'22, Best Paper Nomination)

- By observing the number of performed context switches in each run time, our design adaptively adjusts the checkpointing interval to achieve a good balance between the execution progress (performance) and the number of performed checkpoints.

- At runtime, we design a checkpoint checker that (1) determines the necessity of performing checkpoints and (2) conservatively enlarges the checkpointing interval.

- At reboot time, we design a reboot-time reconfiguration procedure that approaches the suitable checkpointing interval according to the execution status learned from previous run times.

- Compared to a state-of-the-art design called ELASTIN, our approach could reduce the execution time by 50.6% under unstable harvesting condition.

Yen-Ting Chen, Han-Xiang Liu, <u>Yuan-Hao Chang</u>, Yu-Pei Liang, and Wei-Kuan Shih, "SACS: A Self-Adaptive Checkpointing Strategy for Microkernel-Based Intermittent Systems" ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), Boston, MA, USA, Aug. 1-3, 2022. (Best Paper Nomination - Top Conference)

## 6. Others

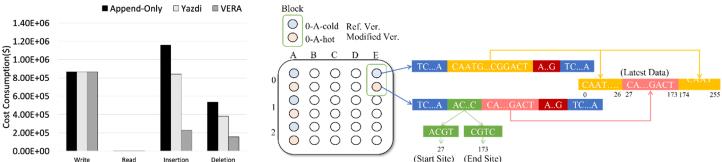

## Write-Cost Reduction for DNA Storage

Observation

(ACM TECS in 2022)

- Accessing digital data over DNA requires a series of extremely time-consuming processes, and the rewriting cost is the predominant cost of DNA data storage system.

- DNA-based storage systems are usually lacking management.

- This work is a pioneer in implementing a management scheme for the DNA-based system and further reducing unnecessary laboratory operations. (ACM TECS in 2022)

- This design advocates a complete management scheme by comparing the latest data and incoming data to know the updated part of the data with minimized reading overhead.

- The idea is to manage the version when the number of versions exceeds the bits provided by the primer.

- lower the total writing bits in each updated operation (i.e., insertion and deletion).

- Compared with the baseline solution, VERA can reduce the writing cost of the DNA storage system by 77%.

<sup>-</sup> Yi-Syuan Lin, Yu-Pei Liang, Tseng-Yi Chen, Yuan-Hao Chang, Shuo-Han Chen, Hsin-Wen Wei, and Wei-Kuan Shih, "How to Enable Index Scheme for Reducing the Writing Cost of DNA Storage on Insertion and Deletion," ACM Transactions on Embedded Computing Systems (TECS), vol. 21, no. 3, pp. 30:1-30:25, May 2022.

## **Research Summary 2021**

# 1. Storage Systems - Flash Drives and SMR Disks

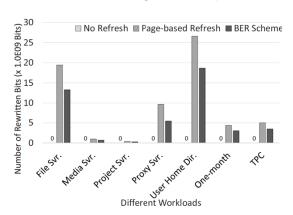

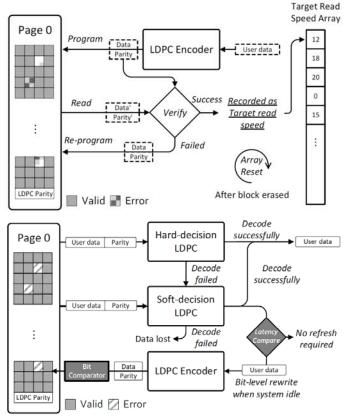

## **Lifetime & Read Optimization for** Bit-alterable Flash (IEEE TCAD in 2021, DAC 2019)

- Observation

- Bit-alterable NAND flash has become a reality to offer the possibility of removing error bits without page-based rewrites.

- However, bit-level rewrites has the similar latency as page-based rewrites

- Goal

- Maximize the read performance with minimal lifetime degradation.

- Main Idea

- Identify different type of bit errors

- Read speed tracking mechanism

- Avoid unnecessary rewrites without lowering throughput

- Sensing latency reduction strategy

Rewritten Bits Reduction: 40.39% Read Speed Improvement: 25.22%

- Shuo-Han Chen, Ming-Chang Yang, and Yuan-Hao Chang, "Optimizing Lifetime Capacity and Read Performance of Bit-Alterable 3D NAND Flash," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 40, no. 2, pp. 218-231, Feb. 2021.

- Shuo-Han Chen, Ming-Chang Yang, and Yuan-Hao Chang, "The Best of Both Worlds: On Exploiting Bit-Alterable NAND Flash for Lifetime and Read Performance Optimization," ACM/IEEE Design Automation Conference (DAC), Las Vegas, Nevada, USA, Jun. 2-6, 2019. (Top Conference)

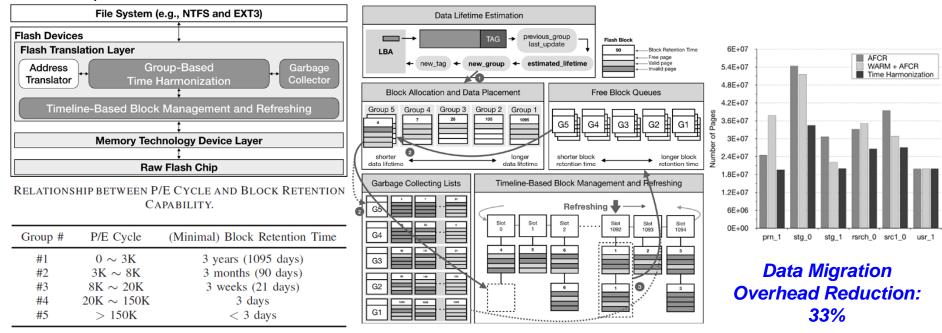

Data Lifetime Estimation

Block Allocation and Data Placement

Garbage Collecting Lists

Free page

-Valid page

Free Block Queues

Timeline-Based Block Management and Refreshing

Refreshing

Harmonization for Data Lifetime and Block Retention time

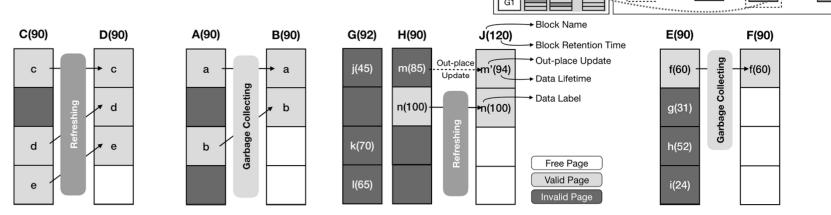

- We propose a <u>Time Harmonization Strategy</u> to harmonize the "retention capability" of flash blocks with different "data lifetime requirement" of the written data (IEEE TC in 2021)

- The mismatch of data lifetime requirement and flash block retention capability could induce additional data migration overhead.

- Goal: (1) Estimate the data lifetime, and efficiently (2) allocate suitable flash blocks to accommodate data in accordance with the block retention capability and the estimated data lifetime.

operations.

Fig. 1. Example of refreshing Fig. 2. Example of garbage collection operations.

Fig. 3. Considering retention capability and data lifetime during refreshing.

Fig. 4. Considering retention capability and data lifetime during garbage collection.

Ming-Chang Yang, Chun-Feng Wu, Shuo-Han Chen, Yi-Ling Lin, Che-Wei Chang, and Yuan-Hao Chang, "On Minimizing Internal Data Migrations of Flash Devices via Lifetime-Retention Harmonization," IEEE Transactions on Computers (TC), vol. 70, no. 3, pp. 428-439, Mar. 2021.

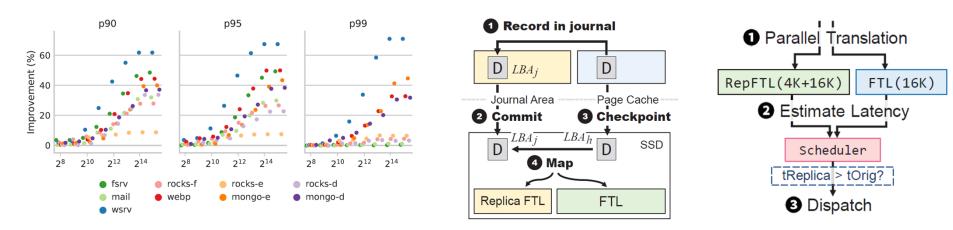

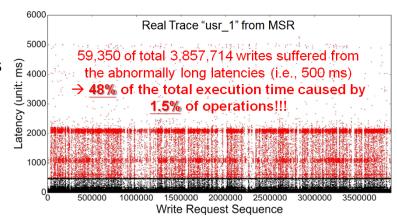

## Reptail – Cutting Storage Tail Latency with Inherent Redundacncy

(DAC 2021)

- Observation

- Increasing SSD density raises read tail latency.

- Data-consistency protection creates data redundancy that is otherwise unused.

- Goal

- Achieve good performance, consistency and high density simultaneously on edge storage

- Main Idea

- Expose SSD to the data identicalness semantics

- Redundancy mapping & Journal defragmentation

- SSD has multiple replicas to fulfill a read request

- Low-overhead table

95th Read Tail Latency Reduction: 20%

<sup>-</sup> Yun-Chih Chen, Chun-Feng Wu, Yuan-Hao Chang, and Tei-Wei Kuo, "Reptail: Cutting Storage Tail Latency with Inherent Redundancy," ACM/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, Dec. 5-9, 2021. (Acceptance rate: 23%) (Top Conference)

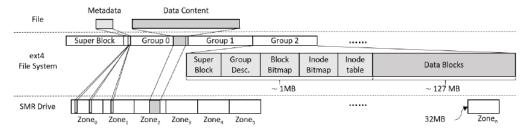

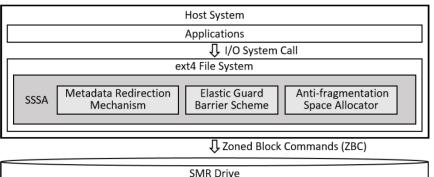

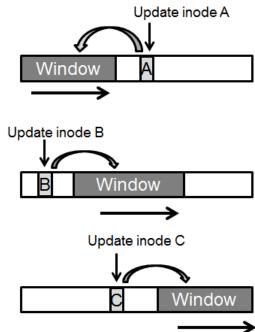

## Secure Deletion for EXT4 File Data and Metadata on SMR-based (ASP-DAC 2021)

- Observation

- The efficiency of secure deletion is highly dependent on the data layout.

- The sequential-write constraint of SMR drive hinder the efficiency of secure deletion.

- However, the small-size nature of file system metadata aggravates the efficiency.

- Goal

- Facilitate the process of securely erasing both the deleted files and their metadata simultaneously.

- Main Idea

- Metadata Redirection Mechanism

- Store file inode along with the file data

- Elastic Guard Barrier Scheme

- Divide SMR zones into smaller segments

- Anti-Fragmentation Space Allocator

- Pack small files into smallest segments

Secure Deletion Latency Reduction: 91.3%

<sup>-</sup> Ping-Xiang Chen, Shuo-Han Chen, Yuan-Hao Chang, Yu-Pei Liang, and Wei-Kuan Shih, "Facilitating the Efficiency of Secure File Data and Metadata Deletion on SMR-based Ext4 File System," ACM/IEEE Asia and South Pacific Design Automation Conference (ASP-DAC), Tokyo, Japan, Jan. 18-21, 2021.

## 2. NVM Main Memory and Storage

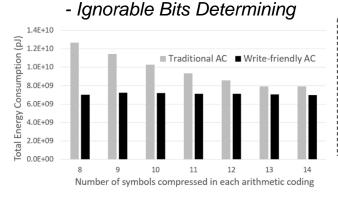

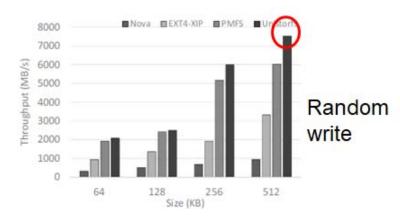

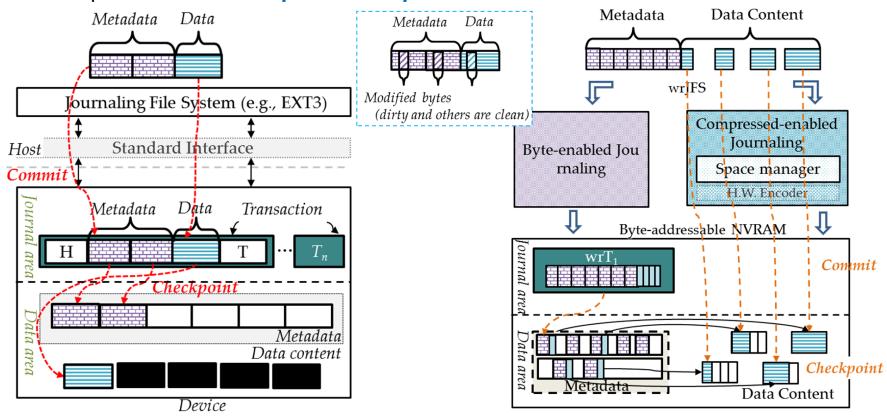

## Write-friendly Arithmetic Coding for NVM

#### Observation

(ASP-DAC 2021)

- Storage-Class Memory technologies and data compression techniques can be used to alleviate the energy consumption of wearable IoT devices

- However, the information gap between the PCM devices and data compression techniques hinders the cooperation among the two techniques for achieving further performance optimization

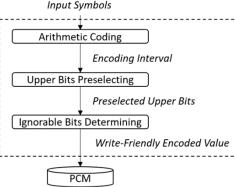

#### Goal

Design an energy-aware and write-friendly arithmetic coding (AC) to improve energy efficiency of PCM

#### Main Idea

- Exploit the property of encoding interval in arithmetic coding to smartly choose an ideal encoded value consists of most ignorable bits, so as to reduce the number of write operations during the compression on PCM

- Upper Bits Preselecting

Encoding Interval = [0.246, 0.24601)Sign Exponent Mantissa (52 bits) IEEE 754 0 011111111100 111101111...... Binary Frac. 0.001  $EV = 2^{-3} = 0.125$ Iter. 1: 0.0011  $EV += 2^{-4} = 0.1875$ Roll back and keep scanning Iter. 4: 0.0011111 EV += **2**<sup>-7</sup> = 0.2421875 EV += 2<sup>-8</sup> = 0.24609375 Iter. 5: 0.0011111**1** 0.00111110**1** Iter. 6:  $EV = 0.2421875 + 2^{-9}$ Iter. 12: 0.00111111011111101 EV +=  $2^{-15}$  = 0.2460021. **Preselected Upper Bits** IEEE 754 0 011 ... 111101111101 Possible Ignorable Bits = 40 *Iter. 1:* 0.0011111011111010...001 EV += 2<sup>-55</sup> 0.00111110111111010...011 EV += 2<sup>-54</sup> Iter. 2: Iter. 38: 0.001.....00111.....1 EV += 2-18 = 0.246009... Iter. 39: 0.001.....01111.....1 EV += 2<sup>-17</sup> = 0.246017...>UB Output EV as the write-friendly encoded value:

Ignorable Bits = 38

Reduce 10.6-44.6% energy, compared to the traditional AC

Yi-Shen Chen, Chun-Feng Wu, Yuan-Hao Chang, and Tei-Wei Kuo, "A Write-friendly Arithmetic Coding Scheme for Achieving Energy-Efficient Non-Volatile Memory Systems," ACM/IEEE Asia and South Pacific Design Automation Conference (ASP-DAC), Tokyo, Japan, Jan. 18-21, 2021.

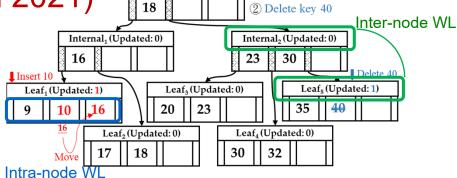

1 Insert key 10

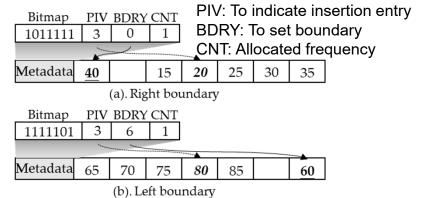

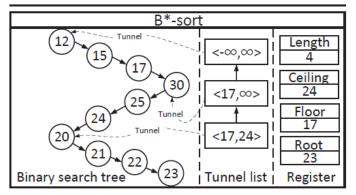

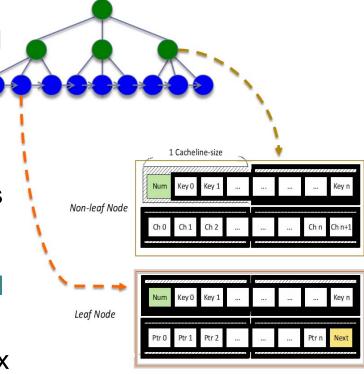

### Wear-leveling-enabled B+-tree over NVM

(IEEE TCAD in 2021)

#### Observations:

The frequent B+-tree key operations result in inter- and intra-node wear-leveling issue.

#### Goal:

To balance the amount of <u>write traffic</u>

<u>within a node space</u> but considers the

<u>global wear-leveling issue over the whole</u>

*NVRAM space* as well

#### Solution:

- Circular node structure:

- To move the start point of insertion in a tree node for evenly distributing the amount of write traffic to each entry space within a node.

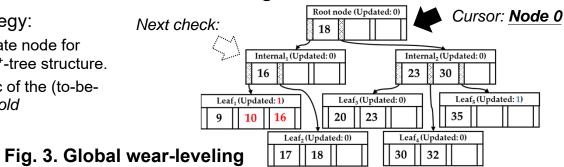

- Global wear-leveling strategy:

- A cursor points a candidate node for swapping in the current B<sup>+</sup>-tree structure.

- The amount of write traffic of the (to-beallocated) node ≥ Threshold

Fig. 1. Our observations

Root node (Updated: 0)

Fig. 2. Circular node structure

<sup>-</sup> Dharamjeet, Tseng-Yi Chen, Yuan-Hao Chang, Chun-Feng Wu, Chi-Heng Lee, and Wei-Kuan Shih, "Beyond Write-reduction Consideration: A Wear-leveling-enabled B+-tree Indexing Scheme over an NVRAM-based Architecture." IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 40, no. 12, pp. 2455-2466, Dec. 2021.

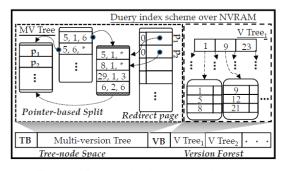

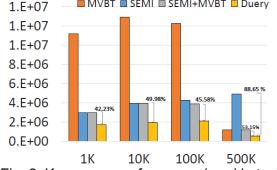

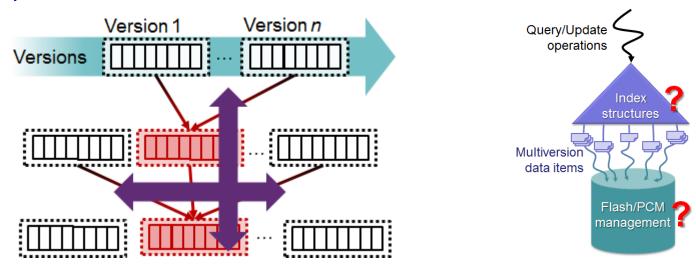

## Write-Reduction Multiversion Scheme to Support Dual-range Query over NVM

Observation

(IEEE TVLSI in 2021)

- multi-version indexing scheme will rewrite duplicate information for achieving an efficient multi-versioned data query, and it will generate a massive amount of write traffics to an NVRAM space

- all multi-version indexing schemes cannot simultaneously provide efficient key and version-range queries

- Goal

- To propose a write-reduction multi-version indexing scheme with efficient dual-rangequery operations over NVRAM-based storage

- Main Idea

- Efficient key-range-query

- Preserves the partial nature of the MVBT (multi-version tree), but reduces the amount of write traffic to NVRAM by a pointer-based split mechanism.

- Efficient version-range-query

- Aggregates the version data belonging to the same index together (version forest)

Fig. 1. Duery indexing scheme

Fig. 2. Key-range performance (read bytes)

Fig. 3. version-range performance (read bytes)

<sup>-</sup> I-Ju Wang, Yu-Pei Liang, Tseng-Yi Chen, Yuan-Hao Chang, Bo-Jun Chen, Hsin-Wen Wei, and Wei-Kuan Shih, "Enabling Write-reduction Multiversion Scheme with Efficient Dual-range Query over NVRAM," IEEE Transactions on Very Large Scale Integration Systems (TVLSI), vol. 29, no. 6, pp. 1244-1256, Jun. 2021.

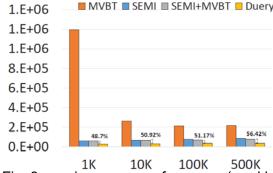

## **Scheduling-aware Prefetching (NVMSA 2021)**

- Observation:

- GPU tasks usually show weak temporal locality because the relation between two warps is independent.

- Applying page replacement approaches on GPU tasks usually suffers from the fast locality saturation issue. Thus, even when larger DRAM is equipped in the GPU, the DRAM hit ratio cannot be further improved.

- Goal:

- Aiming to provide low-cost energy-efficient GPU memory extension systems, this work proposes a <u>scheduler-aware prefetching design</u> to improve system performance.

- Main Idea:

- Memory Manager fully utilizes the information of the internal hardware warp scheduler inside GPU device to perform data prefetching without changing the writing way of the GPU program.

<sup>-</sup> Tse-Yuan Wang, Chun-Feng Wu, Che-Wei Tsao, <u>Yuan-Hao Chang</u>, and Tei-Wei Kuo, "Scheduling-Aware Prefetching: Enabling the PCIe SSD to Extent the Global Memory of GPU Device," IEEE Nonvolatile Memory Systems and Applications Symposium (NVMSA), August 2021.

# 3. Machine Learning Techniques and Processing-in-Memory with NVM

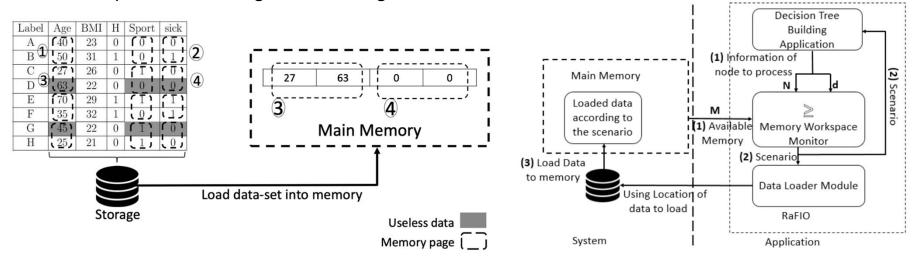

## Random Forest I/O-aware Algorithm

#### Observation

(SAC 2021)

- During training random forest, performance drops significantly when the dataset size is larger than the available memory size.

- Reasons: Randomly bagging data causes unnecessary data movements.

#### Goal

Reduce unnecessary data movement by avoiding loading useless data and smartly selecting the data according to their reuse pattern in the following tree building steps

#### Main Idea

- Decision Tree Building Module: Perform on-demand data loading according to the available memory space.

- Data Loader Module: Pre-process data to easily locate useful data without reading them multiple times during data loading.

#### **Unnecessary Data Movements**

**Unnecessary Data Movements**

<sup>-</sup> Camelia Slimani, Chun-Feng Wu, <u>Yuan-Hao Chang</u>, Stephane Rubini, and Jalil Boukhobza, "RaFIO: A Random Forest I/O-Aware Algorithm," ACM Symposium on Applied Computing (SAC), Gwangiu. South Korea. Mar. 22-26. 2021.

## Space-efficient Graph Placement on ReRAM (ISLPED 2021)

#### Observation

- Placing an adjacency matrix on the crossbar array for accelerating matrix multiplication may lead to unnecessary energy wasting.

- Reason: Elements in the graph adjacency matrix are usually sparse and discrete, and thus extra crossbar OUs are required for processing because of the low-utilization.

#### Goal

Interested in proposing a hardware/software co-design solution to solve the sparse and discrete issues by clustering graph nodes on the crossbar accelerators.

#### Main Idea

Remap and shuffle the original adjacency matrix with being aware of the graph localities.

#### **Low Utilization on Crossbar Accelerator**

#### Design Concept: Remapping and Reshuffling

<sup>-</sup> Ting-Hsuan Lo, Chun-Feng Wu, Yuan-Hao Chang, Tei-Wei Kuo, and Wei-Chen Wang, "Space-efficient Graph Data Placement to Save Energy of ReRAM Crossbar," ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), Virtual Conference, Jul. 26-28, 2021. (Top Conference)

## 4. Intermittent Systems

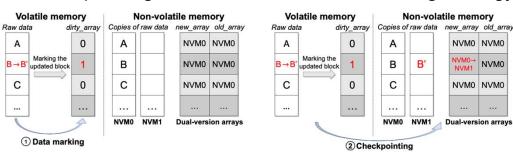

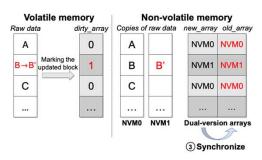

iCheck – Progressive Checkpointing for Intermittent Systems (IEEE TCAD in 2021)

#### Observation:

- Prior checkpointing approaches rely on capacitor measurement (i.e., for checkpoint timing).

- The power failure rate of intermittent devices is often lower nearby the start of a power-on cycle.

#### Goal:

To eliminate the dependency of capacitor since it has relatively shorter lifetime compared with other hardware components in embedded devices.

#### Main idea:

- Power-failure-aware checkpoint triggering that trigger the device to checkpoint progressively, i.e., the checkpointing frequency increases as the time progresses to maximize forward progress.

- Recoverable incremental-state data checkpointing to avoid data inconsistency issue caused by incomplete checkpointing with dual-version data buffering strategy.

(a) Mark the modified data blocks.

(b) Back up the modified memory blocks.

(c) Synchronize the contents of new\_array and old array.

<sup>-</sup> Wen Sheng Lim, Chia-Heng Tu, Chun-Feng Wu, and Yuan-Hao Chang, "iCheck: Progressive Checkpointing for Intermittent Systems," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 40, no. 11, pp. 2224-2236, Nov. 2021.

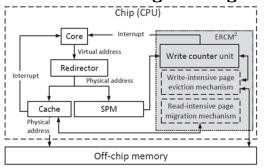

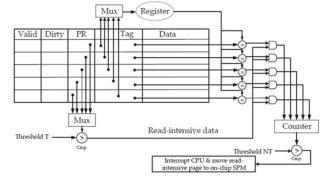

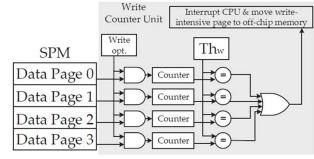

## **Energy-Reduction On-chip Memory Management on Intermittent Systems**

### Motivation (RTAS 2021)

Existing intermittent systems rarely considered the energy consumed during moving data and may waste precious power resource over data movement.

#### Goal

Adopting a STT-RAM-based scratchpad memory and a small volatile cache to be the on-chip memory to enable an energy-reduction intermittent system.

#### Main Challenge

- How to identify the data access pattern in the run time and further distinguish the read/write behavior.

- How to monitor the lifetime of STT-RAM-based SPM

#### Main Idea

- Maximizing the space utilization of both SPM and cache.

- Avoiding moving the write-intensive data into SPM.

Fig. 1 Architecture of hybrid on-chip memory architecture and ERCM<sup>2</sup> scheme.

Fig. 2 augmented cache design

Fig. 3 The proposed write counter unit.

<sup>-</sup> Yu-Pei Liang, Yu-Ting Fang, Shuo-Han Chen, Yen-Ting Chen, Tseng-Yi Chen, Wei-Lin Wang, Wei-Kuan Shih, and Yuan-Hao Chang, "Brief Industry Paper: An Energy-Reduction On-Chip Memory Management for Intermittent Systems," IEEE Real-time and Embedded Technology and Application Symposium (RTAS), Virtual Conference, May 18-21, 2021. (Top Conference)

## **Research Summary 2020**

# 1. Storage Systems - Flash Drives and SMR Disks

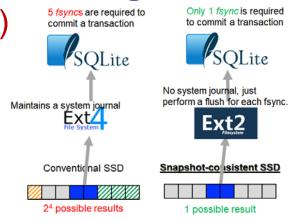

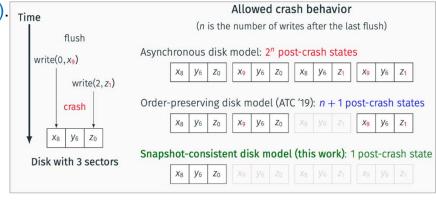

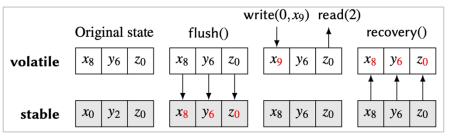

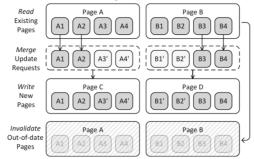

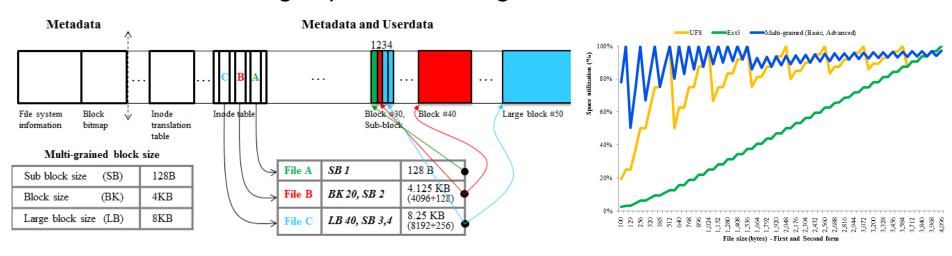

### Crash Recovery Support from the Storage Level

• This is a verified Snapshot-Consistent

Flash Translation Layer (SCFTL) to guarantee determinized time on recovering a flash drive to the state right before the last flush.

- This is the first attempt to leverage formal verification techniques to ensure the correctness of a complex FTL implementation.

- SCFTL is the first work providing a determinized storage crash recovery mechanism to enable a more efficient design of upper layers in the storage stack (e.g., the file system or database

- SYSTEM) is accepted and published in OSDI 2020 (17.6%).

- The first OSDI from Taiwan in the past 26 years.

- SCFTL is available at: https://github.com/yunshengtw/scftl

- 50% of OSDI'20 papers come from MIT, Berkley, and CMU.

- More than 25% of OSDI paper comes from huge companies, e.g., Google, Amazon, Facebook

#### **Existing non-determinizied work vs. SCFTL**

**Design Concept of the proposed SCFTL**

<sup>-</sup> Yun-Sheng Chang, Yao Hsiao, Tzu-Chi Lin, Che-Wei Tsao, Chun-Feng Wu, <u>Yuan-Hao Chang</u>, Hsiang-Shang Ko, and Yu-Fang Chen, "Determinizing Crash Behavior with a Verified Snapshot-Consistent Flash Translation Layer" USENIX Symposium on Operating Systems Design and Implementation (OSDI), Banff, Alberta, Canada, Nov. 4-6, 2020. (Acceptance rate: 17.6% (70/398)) (Top Conference)

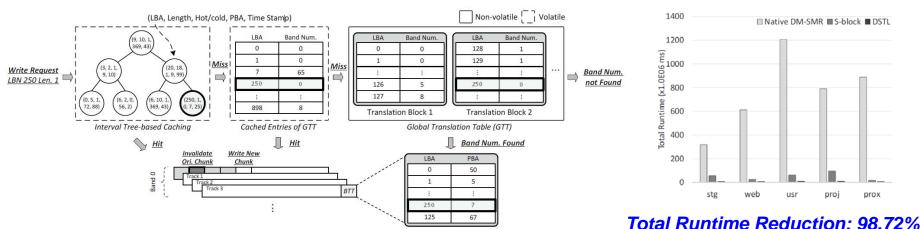

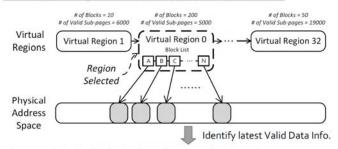

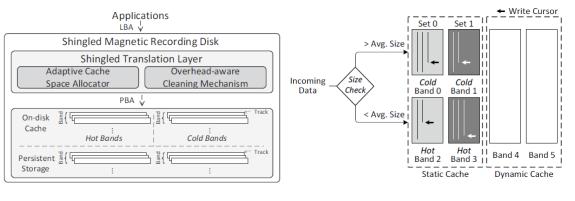

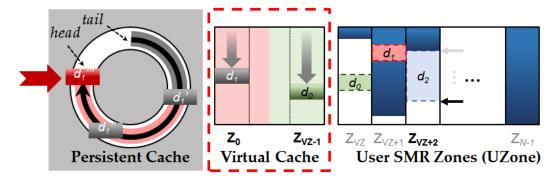

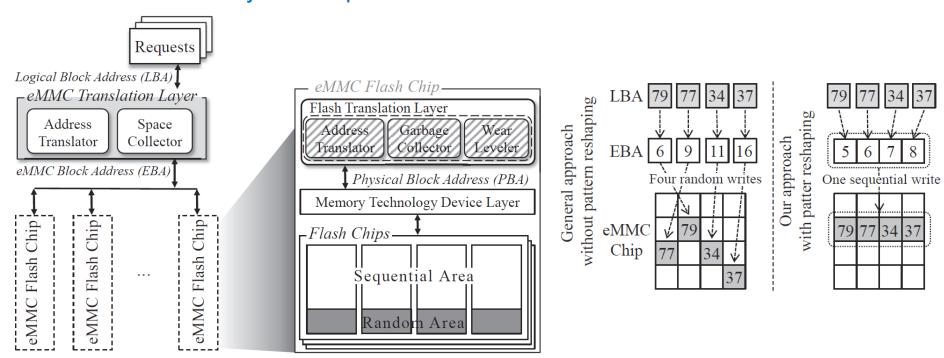

# A Demand-based Shingled Translation Layer for SMR Disks (ACM TECS in 2020)

#### Observation

- Drive-managed SMR (DM-SMR) employs a shingled translation layer (STL) to hide its inherent sequential-write constraint from the host software.

- However, the access pattern and the data update frequency of incoming workloads are not considered during managing STL

#### Goal

Enhance the access performance of DM-SMR via considering the access pattern and update frequency at the same time.

#### Main Idea

- Lower the overhead during updating STL

- Two-layer mapping scheme & Interval tree-based caching

- Separate hot/cold data to lower overhead during space reclaim

- Hotness-aware band allocator & Neighboring invalid space reclamation

- Yi-Jing Chuang, Shuo-Han Chen, <u>Yuan-Hao Chang</u>, Yu-Pei Liang, Hsin-Wen Wei, and Wei-Kuan Shih, "DSTL: A Demand-based Shingled Translation Layer for Enabling Adaptive Address Mapping on SMR Drives," ACM Transactions on Embedded Computing Systems (TECS), vol. 19, no. 4, pp. 25:1-25:21, Jul. 2020.

BTT of Band 0

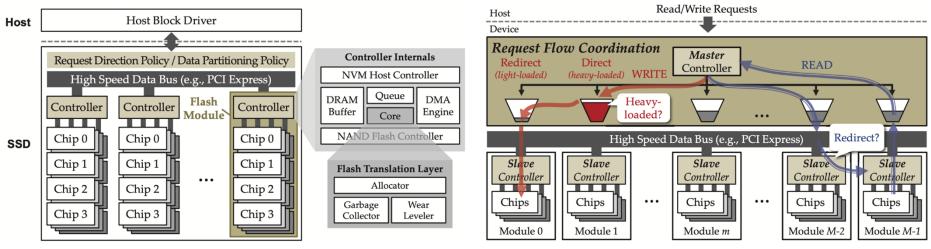

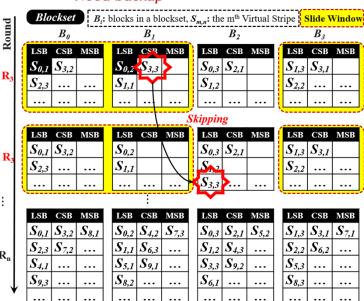

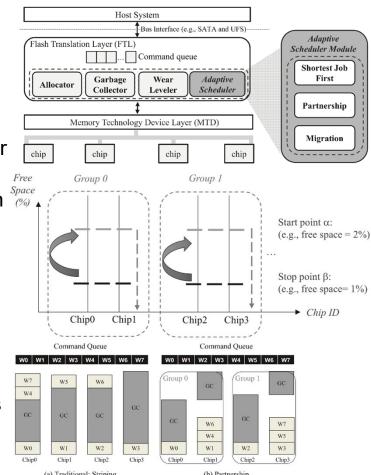

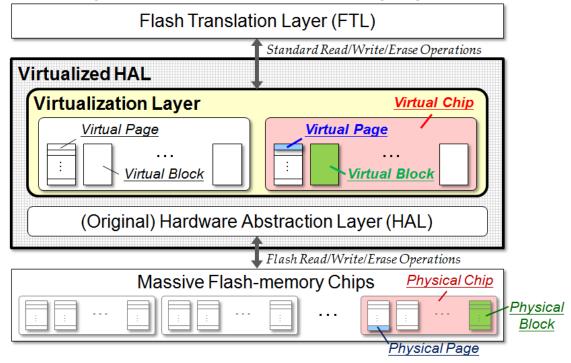

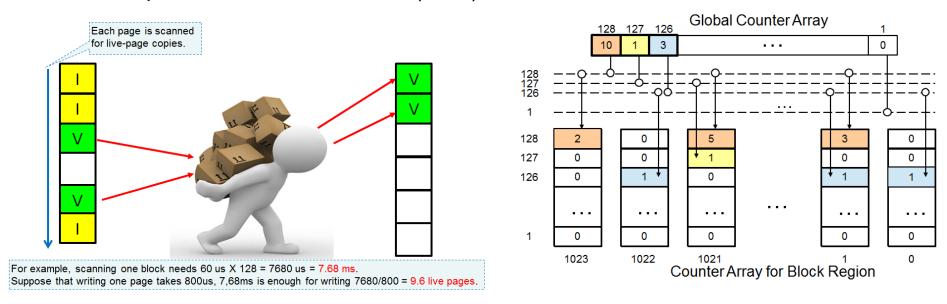

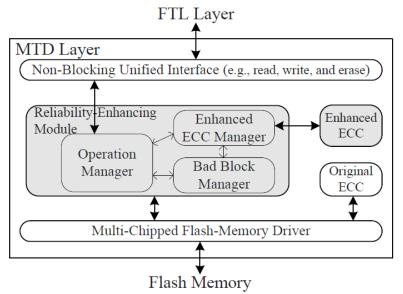

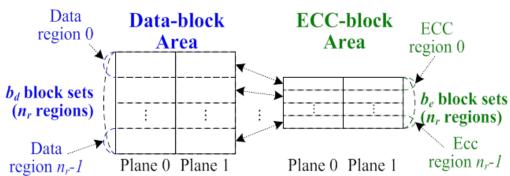

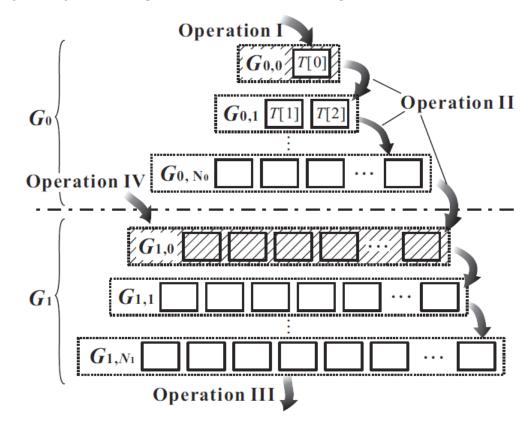

## Request Flow Coordination for Largescale Flash Storage

- We propose a <u>Request Floe Coordination Design</u> to appropriately control and throttle the I/O request flows over the increasingly complicated SSD internal organization with scalable and manageable coordination overhead. (IEEE TC in 2020)

- Due to the interface and architecture changes, we aim to achieve good design scalability to facilitate the device development when the scale of SSDs keeps growing. This work tends to embrace the new many-chip and many-core SSD architecture

- Avoid overloading any sub-module of the SSD by making a good use of the abundant internal resources, so that the request response time can be effectively reduced and the overall SSD performance can be significantly improved.

**Architecture of Many Chips & Cores**

**Request Flow Coordination Design**

<sup>-</sup> Ming-Chang Yang, Yuan-Hao Chang, Tei-Wei Kuo, and Chun-Feng Wu, "Request Flow Coordination for Growing-Scale Solid-State Drives," IEEE Transactions on Computers (TC), vol. 69, no. 6, pp. 832-843. Jun. 2020.

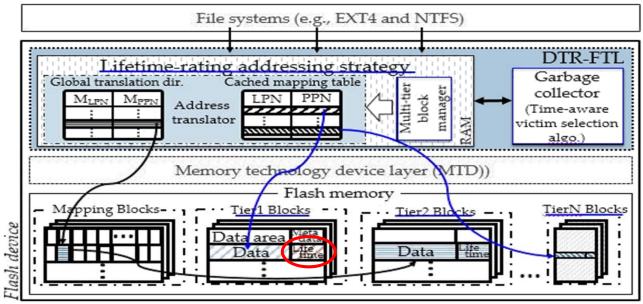

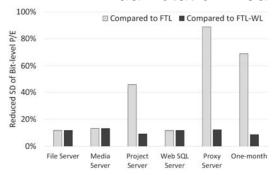

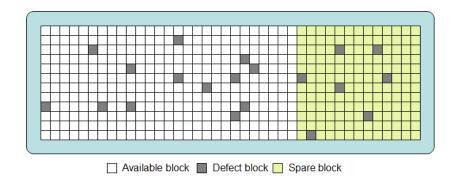

## Cutting Expired Data with Zero Overhead in Flash Storage (DAC 2020)

#### Observation

- There are many disused (or expired) data in the flash storage device but still be treated as valid data. The unnecessary page copying during GC process cause huge extra overhead.

- Once the host system can provide the data lifetime information, we can directly identify data is expired or not.

#### Goal and Method

- We proposed a dual-time referencing FTL design (DTR-FTL). Our DTR-FTL will aggregate data together based on the data lifetime information and block retention time.

- Automatically cut out expired via lifetime information.

- Using those low retention time blocks (high P/E cycles blocks) to record short lifetime data.

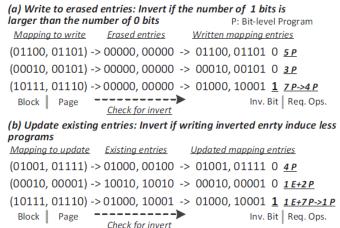

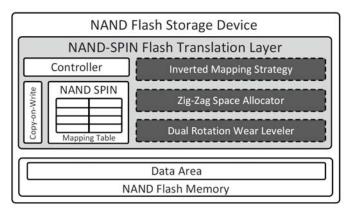

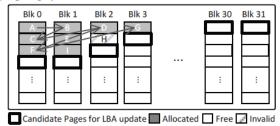

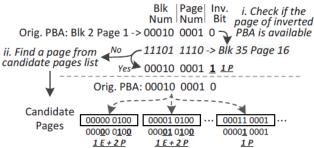

## **Bit-Level Wearing for NAND-SPIN**

- Observation

- NAND-SPIN memory resolved the high program latency & inefficient power consumption of 1T1MTJ STT-MRAM

- Unique characteristic: A string of NAND-SPIN cells can be updated multiple times before being erased

- Goal

- Alleviate the bit-level uneven wearing issue by allowing more bits to be programed before being erased

- Main Idea

- Avoid both uneven intra-entry wearing and excessive string-based erases

- Inverted mapping strategy & Zig-Zag space allocator

- Perform wear leveling at both bit and entry level

- Dual rotation wear leveler

#### Bit-level P/E

Std. Reduction: 40.11%

Mean Reduction: 9.86%

### (NVMSA 2020)

#### (a) Zig-Zag Space Allocation

#### (b) Example of allocating page for a logical page update

## Challenges of Secure Deletion in Storages

This work aims at evaluating and comparing the implementation challenges of secure data deletion and sanitization techniques.

- State-of-the-art designs that have been paid to pursue better efficiency, verifiability, and portability for both HDDs and SSDs are summarized

- > The pros and cons on implementing "secure deletion" of different techniques are discussed

- E.g., encryption-based, erasure-based, overwriting-based, and mixed techniques

| Secure Deletion Approach         | Implemented Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Deletion<br>Granularity | Secure Deletion<br>Efficiency | Endurance            | Overhead                        |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------|----------------------|---------------------------------|--|--|--|

|                                  | File system Per-block Medium-High Unchanged Encryption/Decryption overheads File system Per-block Medium-High Unchanged Encryption/Decryption overheads  File system Per-block Medium-High Unchanged Encryption/Decryption overheads  Frasure-based  Ing [23] User level Per-block Low Large wear Performance overhead Multiple level Per-block Medium Some wear Performance overhead Controller level Per-block Medium-high Some wear Large deletion overhead  Overwriting-based  25] Controller level Per-block Medium Unchanged Impracticable for SSDs Controller and device levels Per-page Medium-high Small wear Data disturbance Controller and device levels Per-page Medium-high Small wear Data disturbance  Optimization on SSDs  Controller level Per-block High Unchanged Encryption/Decryption etion [15] Controller level Per-block High Unchanged Overheads Controller level Per-block High Unchanged Overheads Controller level Per-block High Unchanged Overheads Controller level Per-page and block High Unchanged Overheads |                         |                               |                      |                                 |  |  |  |

| ASDEFS [3]                       | File system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Per-block               | Medium-High                   | Unchanged            | Key management;                 |  |  |  |

| DNEFS [22]                       | File system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Per-block               | Medium-High                   | Unchanged            | Encryption/Decryption overheads |  |  |  |

| Erasure-based                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |                               |                      |                                 |  |  |  |

| Purging and Ballooning [23]      | User level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Per-block               | Low                           | Large wear           | Performance overhead            |  |  |  |

| TrueErase [7]                    | Multiple level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Per-block               | Midium                        | Some wear            | Performance overhead            |  |  |  |

| SAFE [32]                        | Controller level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Per-block               | Medium-high                   | Some wear            | Large deletion overhead         |  |  |  |

|                                  | User level Per-block Low Large wear Performance overhead Multiple level Per-block Midium Some wear Performance overhead Controller level Per-block Medium-high Some wear Large deletion overhead  Overwriting-based  Controller level Per-block Medium Unchanged Impracticable for SSDs Controller and device levels Per-page Medium-high Small wear Data disturbance  Controller and device levels Per-page Medium-high Small wear Data disturbance  Optimization on SSDs  Controller level Per-block High Unchanged Key management;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         |                               |                      |                                 |  |  |  |

| ATA commands [2], [25]           | Controller level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Per-block               | Medium                        | Unchanged            | Impracticable for SSDs          |  |  |  |

| Scrubbing [31]                   | Controller and device levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Per-page                | Medium-high                   | Small wear           | Data disturbance                |  |  |  |

| Partial-scrubbing [13]           | Controller and device levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Per-page                | Medium-high                   | Small wear           | Data disturbance                |  |  |  |

|                                  | ial-scrubbing [13] Controller and device levels Per-page Medium-high Small wear Data disturbance Optimization on SSDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         |                               |                      |                                 |  |  |  |

| ErasuCrypto [19]                 | Controller level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Per-block               | High                          | Unchanged            | Key management;                 |  |  |  |

| Temperature-aware [17]           | Controller level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Per-block               | High                          | Unchanged            | Encryption/Decryption           |  |  |  |

| Selectively secure deletion [15] | Controller level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Per-block               | High                          | Unchanged            | overheads                       |  |  |  |

| Scrubbing-aware [28]             | Controller and device levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Per-page and block      | High                          | Some wear            | Additional memory overhead      |  |  |  |

| Fast sanitization [18]           | Controller and device levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Per-page                | Extremely high                | Extremely small wear | Very small performance overhead |  |  |  |

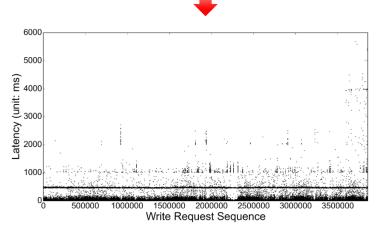

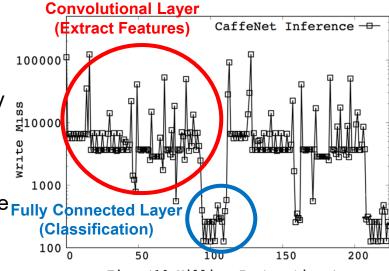

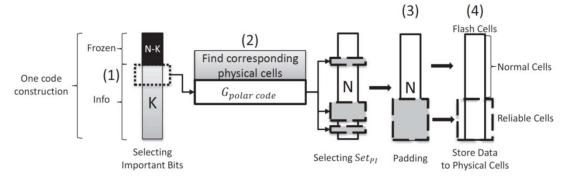

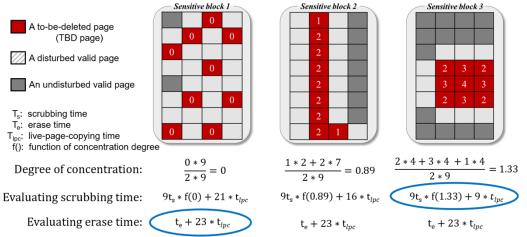

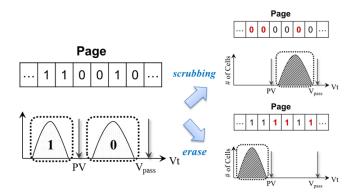

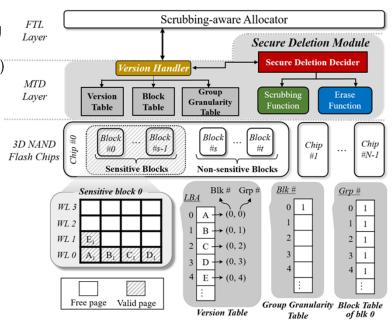

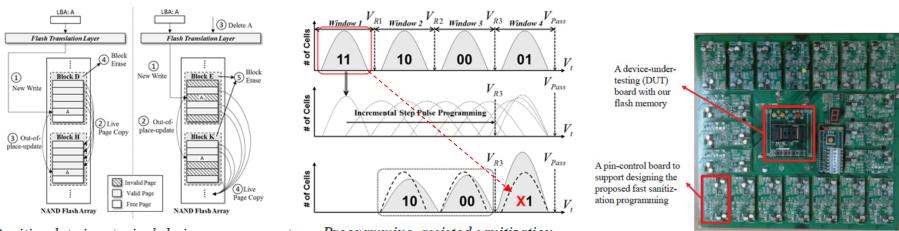

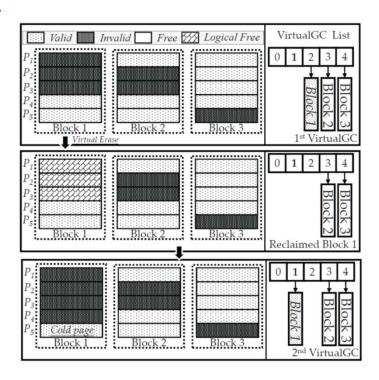

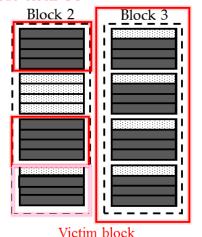

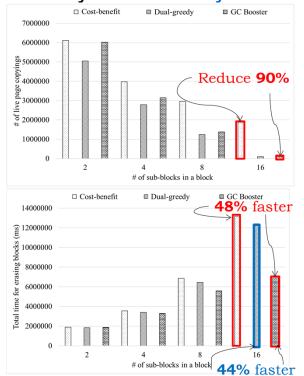

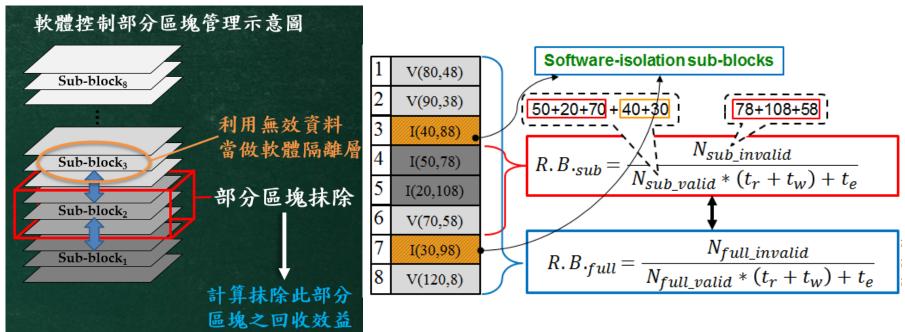

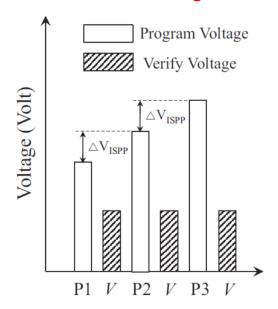

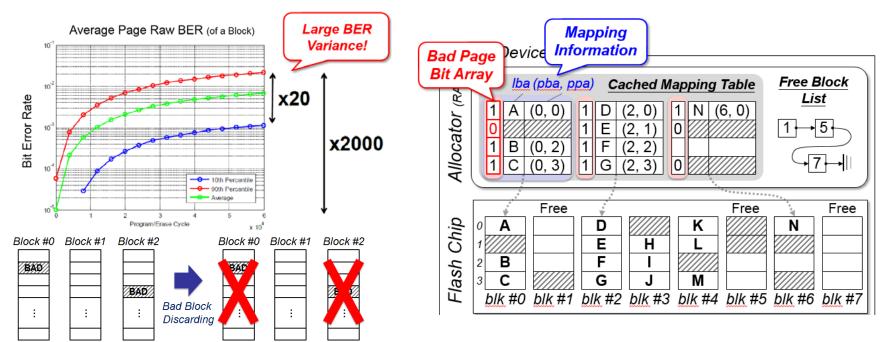

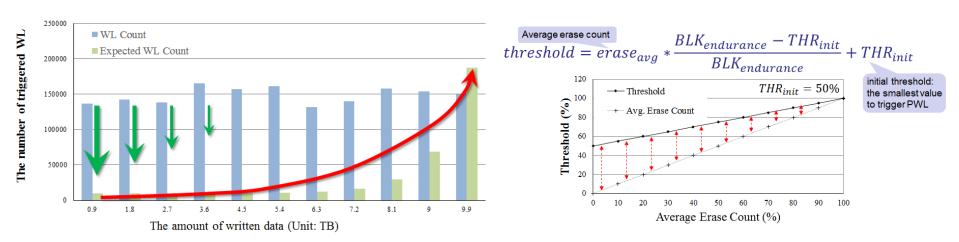

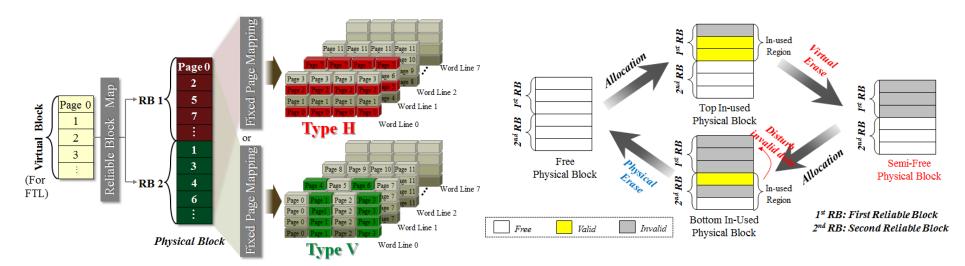

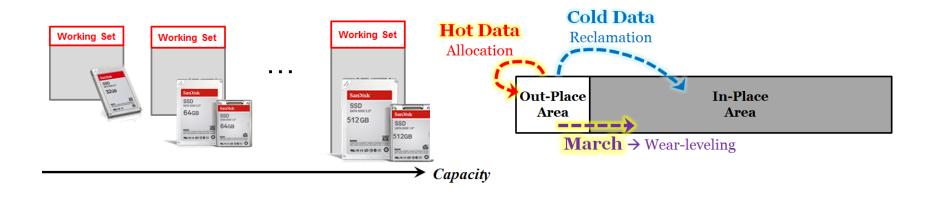

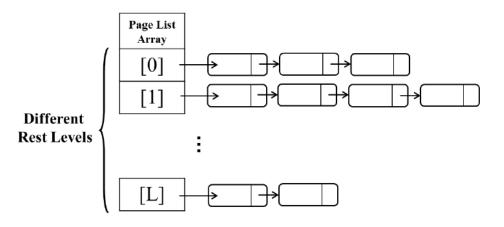

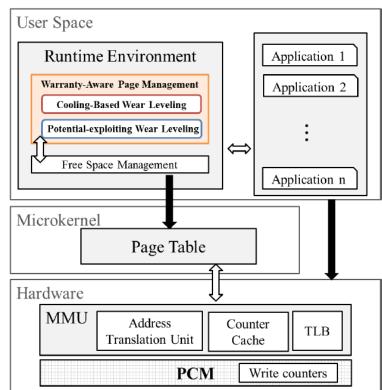

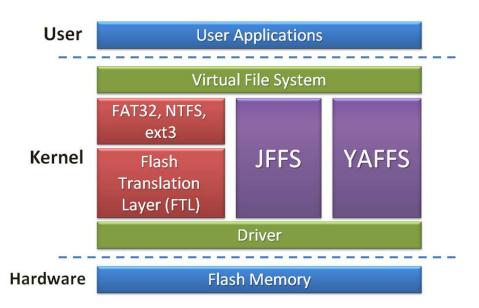

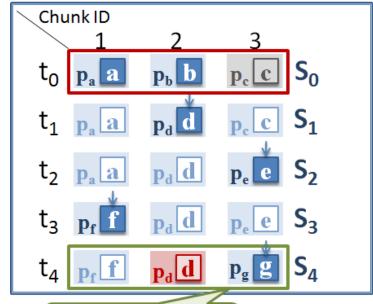

| Instantaneous sanitization [29]  | Controller and device levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Per-page                | Extremely high                | Extremely small wear | Space utilization               |  |  |  |